我使用是是普中科技的28335开发板。因为要存储数组数据,所以外扩了SRAM。定义了ZONE7区域,并将数组变量指定存储到该区域。在定时器中断程序中给该变量赋值,但是在Expression中观察,赋值过后的变量值仍然会跳变,而且在memory browser中观察该值,好像并没有赋值成功。以下是相关程序及截图:

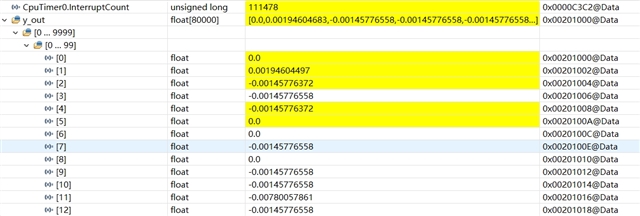

图一CpuTimer0.InterruptCount已经超过了数组的范围,然后y_out数据发生了跳变(黄色就代表发生了变化)。(已经排除了外部SRAM地址线和数据线与其他功能项接口复用的问题)

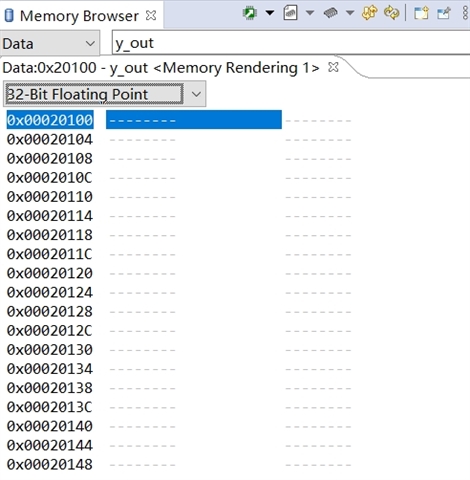

图二在memory browser中观察y_out数据空间,但是并没有值被赋值进来?

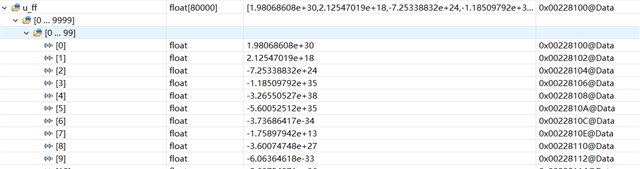

图三我给u_ff初始化赋值,但是并没有赋值成功,应该怎么初始化赋值呢?

//=============================

// ----------- time.c----------------

#pragma DATA_SECTION(y_out,"ZONE7DATA");

volatile float y_out[80000] = {0.0};

#pragma DATA_SECTION(u_ff,"ZONE7DATA");

volatile float u_ff[80000] = {

{0},

{-5.48168582231433},

{-28.0960788724069},

{-33.2755709254560},

{-28.4364523855368}

};

interrupt void TIM0_IRQn(void){

//省略其他无关代码

y_out[CpuTimer0.InterruptCount] = Pos;

CpuTimer0.InterruptCount++;

}

//==============================

// --------------28335_RAM_lnk.cmd----------------

PAGE 1 :

ZONE7B : origin = 0x201000, length = 0x0F0000 /* XINTF zone 7 */

SECTIONS

ZONE7DATA : > ZONE7B, PAGE = 1

//==============================

// -------------init_zone7.c --------------------------

void init_zone67(void)

{

EALLOW;

// Make sure the XINTF clock is enabled

SysCtrlRegs.PCLKCR3.bit.XINTFENCLK = 1;

EDIS;

// Configure the GPIO for XINTF with a 16-bit data bus

// This function is in DSP2833x_Xintf.c

InitXintf16Gpio();

// All Zones---------------------------------

// Timing for all zones based on XTIMCLK = SYSCLKOUT

EALLOW;

XintfRegs.XINTCNF2.bit.XTIMCLK = 0;

// Buffer up to 3 writes

XintfRegs.XINTCNF2.bit.WRBUFF = 3;

// XCLKOUT is enabled

XintfRegs.XINTCNF2.bit.CLKOFF = 0;

// XCLKOUT = XTIMCLK

XintfRegs.XINTCNF2.bit.CLKMODE = 0;

XintfRegs.XTIMING7.bit.XWRLEAD = 3;

XintfRegs.XTIMING7.bit.XWRACTIVE = 7;

XintfRegs.XTIMING7.bit.XWRTRAIL = 3;

// Zone read timing

XintfRegs.XTIMING7.bit.XRDLEAD = 3;

XintfRegs.XTIMING7.bit.XRDACTIVE = 7;

XintfRegs.XTIMING7.bit.XRDTRAIL = 3;

// don't double all Zone read/write lead/active/trail timing

XintfRegs.XTIMING7.bit.X2TIMING = 1;

// Zone will not sample XREADY signal

XintfRegs.XTIMING7.bit.USEREADY = 1;

XintfRegs.XTIMING7.bit.READYMODE = 1;

// 1,1 = x16 data bus

// 0,1 = x32 data bus

// other values are reserved

XintfRegs.XTIMING7.bit.XSIZE = 3;

EDIS;

//Force a pipeline flush to ensure that the write to

//the last register configured occurs before returning.

asm(" RPT #7 || NOP");

}