你好,我在配置280039C芯片的MCAN的过滤器时,发现第一个过滤器的sfid2无法正常工作,请问是什么原因呢?具体配置如下:

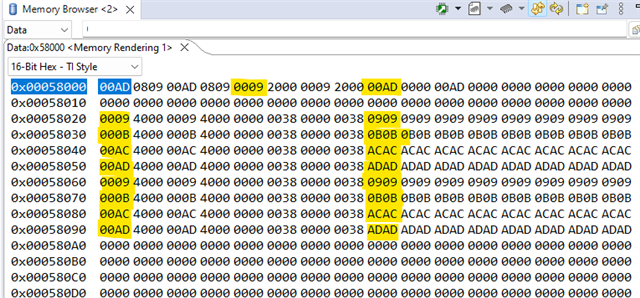

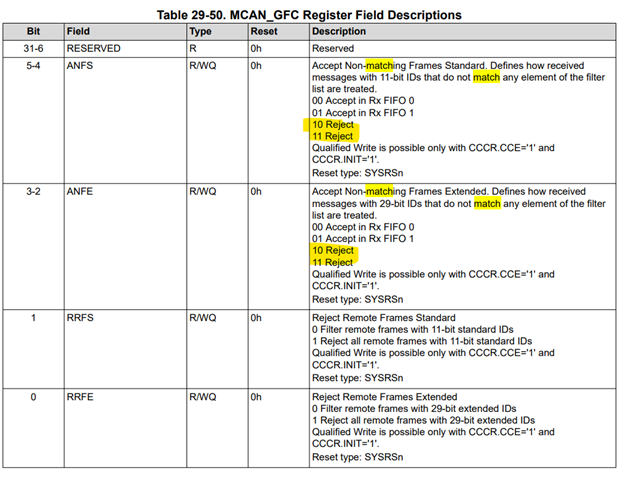

ConfigParams.filterConfig.anfs = 2U;

MCAN_config(MCANA_DRIVER_BASE, &ConfigParams );

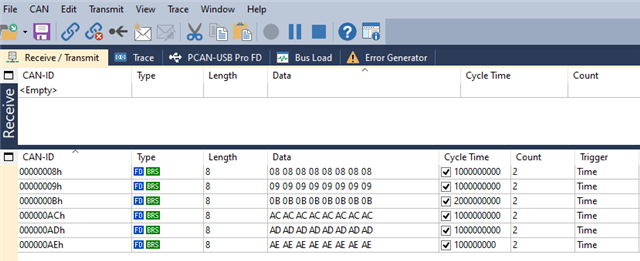

StdFilterElement.sfid1 = 0x009U;

StdFilterElement.sfid2 = 0x0ADU;

StdFilterElement.sfec = 1U;

StdFilterElement.sft = 1U;

MCAN_addStdMsgIDFilter(MCANA_DRIVER_BASE, 0U, &StdFilterElement);

配置如上,sfid1正常工作,但是sfid2无法工作,请问是什么原因呢