各位先進好

F5419A 有4個UART PORT.

使用XT2 (8MHZ) 做為CLOCK SOURCE.

單獨使用 UART0.UART2,UART3通訊115200bps 都正常

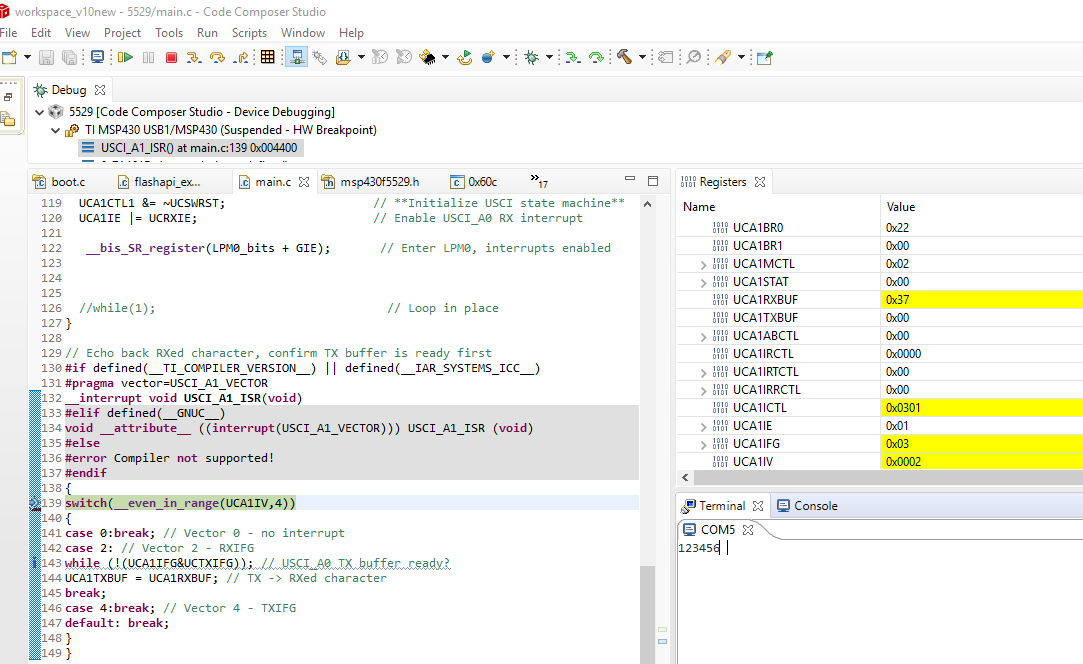

一旦啟用UART1, 全部UART失效.

且 P11.2 輸出從8MHZ 變1MHZ?

請問 先進 是否有建議 ??000_UART1_FAIL_XT2.pdf

//******************************************************************************

// MSP430F543xA Demo - USCI_A0, 115200 UART Echo ISR, DCO SMCLK

//

// Description: Echo a received character, RX ISR used. Normal mode is LPM0.

// USCI_A0 RX interrupt triggers TX Echo.

// Baud rate divider with 1048576hz = 1048576/115200 = ~9.1 (009h|01h)

// ACLK = REFO = ~32768Hz, MCLK = SMCLK = default DCO = 32 x ACLK = 1048576Hz

// See User Guide for baud rate divider table

//

// MSP430F5438A

// -----------------

// /|\| |

// | | |

// --|RST |

// | |

// | P3.4/UCA0TXD|------------>

// | | 115200 - 8N1

// | P3.5/UCA0RXD|<------------

//

// M. Morales

// Texas Instruments Inc.

// June 2009

// Built with CCE Version: 3.2.2 and IAR Embedded Workbench Version: 4.11B

//******************************************************************************

// UART0~UART3 �P�ɱҰ� . �̧ǭӧO��X ���\

#include <msp430.h>

#define PUMP P1OUT ^= 0x01 //BUZ �w��DOG

unsigned int KI;

void SetVcoreUp (unsigned int level);

int main(void)

{

WDTCTL = WDTPW + WDTHOLD; // Stop WDT

P11DIR |= 0x07; // ACLK, MCLK, SMCLK set out to pins

P11SEL |= 0x07; // P11.0,1,2=8MHZ

//===========================STEP 2 ===============================

SetVcoreUp(PMMCOREV_1);

SetVcoreUp(PMMCOREV_2); // Set VCore to 1.8MHz for 20MHz

P5SEL |= 0x0C; // ###### Port select XT2

UCSCTL6 &= ~XT2OFF; // ###### Enable XT2 #################

UCSCTL3 |= SELREF_2; // FLLref = REFO Since LFXT1 is not used,

// sourcing FLL with LFXT1 can cause XT1OFFG flag to set

UCSCTL4 |= SELA_2; // ACLK=REFO,SMCLK=DCO,MCLK=DCO

// Loop until XT1,XT2 & DCO stabilizes

do

{

UCSCTL7 &= ~(XT2OFFG + XT1LFOFFG + XT1HFOFFG + DCOFFG);

// Clear XT2,XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}while (SFRIFG1&OFIFG); // Test oscillator fault flag

//UCSCTL6 &= ~XT2DRIVE0; // Decrease XT2 Drive according to

PUMP; // expected frequency

//�ʥH�U�T�� �L�k����...........

for(KI=0;KI<50000;KI++){ //�]��í�w�ɶ�����. �ɭPSMCLK ��������

PUMP;

PUMP;

//�ҥH�W�[��LOOP. �Y�i�bXT2 í�w��.�~�ií�w����SMCLK=MCLK=XT2

}

// %%% ���B�i�H�M�w SMCLK�PMCLK �W�v=10MHZ �� 1MHZ %%%

//UCSCTL4 |= SELS_5 + SELM_5; // SMCLK=XT2=8MHZ MCLK=10MHZ �i�H�ߧY����P1.1 ��X�g��=1.6us

UCSCTL4 |= SELS_5; // SMCLK=XT2=8MHZ MCLK=1MHZ �i�H�ߧY����P1.1 ��X�g��=16us

PUMP;

for(KI=0;KI<50000;KI++){ //�]��í�w�ɶ�����. �ɭPSMCLK ��������

PUMP;

PUMP;

//�ҥH�W�[��LOOP. �Y�i�bXT2 í�w��.�~�ií�w����SMCLK=MCLK=XT2

}

//

P3SEL = 0x30; // P3.4,5 = USCI_A0 TXD/RXD

UCA0CTL1 |= UCSWRST; // **Put state machine in reset**

UCA0CTL1 |= UCSSEL_2; // SMCLK

UCA0BR0 = 69; // 1MHz 115200 (see User's Guide)

UCA0BR1 = 0; // 1MHz 115200

UCA0MCTL |= UCBRS_1 + UCBRF_0; // Modulation UCBRSx=1, UCBRFx=0

UCA0CTL1 &= ~UCSWRST; // **Initialize USCI state machine**

/*

//

P5SEL = 0xC0; // P5 = USCI_A1 TXD/RXD

UCA1CTL1 |= UCSWRST; // **Put state machine in reset**

UCA1CTL1 |= UCSSEL_2; // SMCLK

UCA1BR0 = 69; // 1MHz 115200 (see User's Guide)

UCA1BR1 = 0; // 1MHz 115200

UCA1MCTL |= UCBRS_1 + UCBRF_0; // Modulation UCBRSx=1, UCBRFx=0

UCA1CTL1 &= ~UCSWRST; // **Initialize USCI state machine**

*/

//

P9SEL = 0x30; // P9 = USCI_A2 TXD/RXD

UCA2CTL1 |= UCSWRST; // **Put state machine in reset**

UCA2CTL1 |= UCSSEL_2; // SMCLK

UCA2BR0 = 69; // 1MHz 115200 (see User's Guide)

UCA2BR1 = 0; // 1MHz 115200

UCA2MCTL |= UCBRS_1 + UCBRF_0; // Modulation UCBRSx=1, UCBRFx=0

UCA2CTL1 &= ~UCSWRST; // **Initialize USCI state machine**

//

P10SEL = 0x30; // P10 = USCI_A3 TXD/RXD

UCA3CTL1 |= UCSWRST; // **Put state machine in reset**

UCA3CTL1 |= UCSSEL_2; // SMCLK

UCA3BR0 = 69; // 1MHz 115200 (see User's Guide)

UCA3BR1 = 0; // 1MHz 115200

UCA3MCTL |= UCBRS_1 + UCBRF_0; // Modulation UCBRSx=1, UCBRFx=0

UCA3CTL1 &= ~UCSWRST; // **Initialize USCI state machine**

while(1){

while(!(UCA0IFG & UCTXIFG)); //���� UART ��X�\��

UCA0TXBUF=0x41; //���� UART ��X�\��

while(!(UCA1IFG & UCTXIFG)); //���� UART ��X�\��

UCA1TXBUF=0x42; //���� UART ��X�\��

while(!(UCA2IFG & UCTXIFG)); //���� UART ��X�\��

UCA2TXBUF=0x43; //���� UART ��X�\��

while(!(UCA3IFG & UCTXIFG)); //���� UART ��X�\��

UCA3TXBUF=0x44; //���� UART ��X�\��

__delay_cycles(1000000); //���� UART ��X�\��

}

}

void SetVcoreUp (unsigned int level) {

// Open PMM registers for write

PMMCTL0_H = PMMPW_H;

// Set SVS/SVM high side new level

SVSMHCTL = SVSHE + SVSHRVL0 * level + SVMHE + SVSMHRRL0 * level;

// Set SVM low side to new level

SVSMLCTL = SVSLE + SVMLE + SVSMLRRL0 * level;

// Wait till SVM is settled

while ((PMMIFG & SVSMLDLYIFG) == 0);

// Clear already set flags

PMMIFG &= ~(SVMLVLRIFG + SVMLIFG);

// Set VCore to new level

PMMCTL0_L = PMMCOREV0 * level;

// Wait till new level reached

if ((PMMIFG & SVMLIFG))

while ((PMMIFG & SVMLVLRIFG) == 0);

// Set SVS/SVM low side to new level

SVSMLCTL = SVSLE + SVSLRVL0 * level + SVMLE + SVSMLRRL0 * level;

// Lock PMM registers for write access

PMMCTL0_H = 0x00;

}