Other Parts Discussed in Thread: SYSCONFIG

高优先级中断,阻止低优先级中断状态更新,是BUG吗???

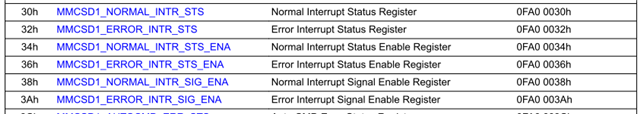

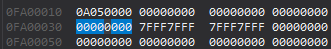

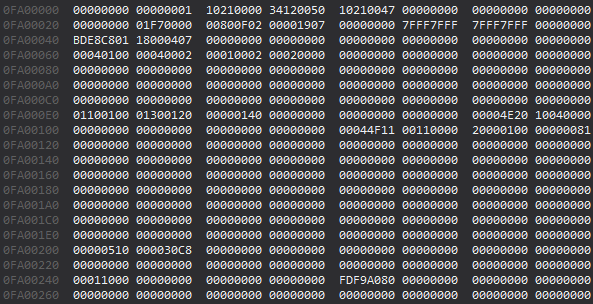

R5程序中,PRU和MMC中断,PRU优先级比MMC高,在PRU中断程序里,与MMC外设通讯,MMCSD1_NORMAL_INTR_STS(Normal Interrupt Status Register,0FA0 0030h)和MMCSD1_ERROR_INTR_STS(Error Interrupt Status Register,0FA0 0032h)寄存器,里面的中断状态没有更新,请问是怎么回事?所有中断,我都Enable了的。