主题中讨论的其他器件:SysConfig

工具与软件:

您好、TI 专家:

我对 CBA9的诊断措施有疑问-无效事务的错误代码。 安全手册解释了这种诊断措施由硬件执行并会生成总线错误。 那么:

可以通过 R5FSS0_CORE0_INTR_IN_133中断来接收该诊断措施吗? 如果是、是否需要启用其他寄存器(例如 err_intr_enable_set)? 是否需要在中断回调中清除中断?

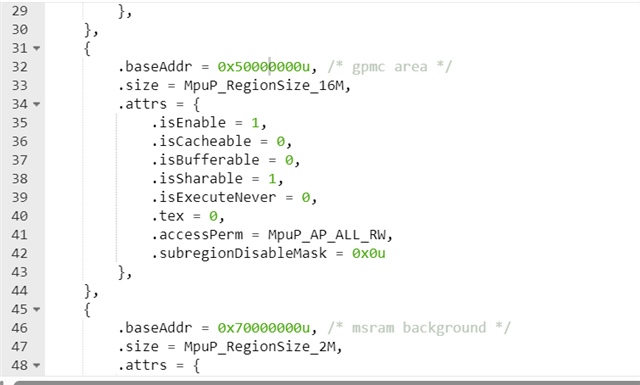

2.我需要测试这种诊断措施。 我是否可以直接将数据写入 PCIe 器件地址(0x69000000)以进行测试(在我的项目中、未使用 PCIe 器件且该器件尚未初始化)。 但是、在我的测试中、在尝试写入后、发生了数据中止异常。

测试日志:

数据中止:反向跟踪:

请使用:addr2line -e rtthread.elf -a -f ffffffff828e9a60[17103](带反向跟踪):回溯:未知符号地址 ffffffffffffffffff828e9a60

[17103] W/ backtrace: unred: index not founded ffffffff828e9a60.

执行:

R00:0x00000000 R01:0x69000000 R02:0xffffffff828e9a40 R03:0xffffffffffffffffffffff

r04:0xffffffffdeadbeh r05:0xffffffffdeadbeh r06:0xffffffffdeadbeh r07:0xffffffffdeadbeh

R08:0xffffffffdeadbeh R09:0xffffffffdeadbeh R10:0xffffffffdeadbeh

fp :0xffffffdeadbeef ip :0x00000000

SP :0xffffff84001948 LR :0x700b1798 PC :0xffffff828e9a68

CPSR:0x20000013

uint32_t ulTestData = 0U; void* hTransBufAddr = (void*)(CONFIG_PCIE0_OB_REG_L_TEST); memcpy(hTransBufAddr, &ulTestData, sizeof(uint32_t));

如果我的方法有问题、请给我一些指导。 我需要通过事件注入测试该诊断措施。

谢谢!

此致。

Kaijie