大家好

如果我们问 LMK05318、您会介意吗?

您能参考.TCS 文件和示波器图吗?

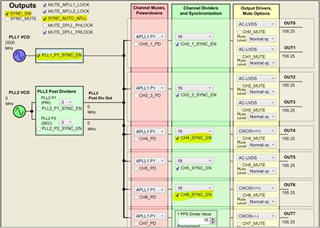

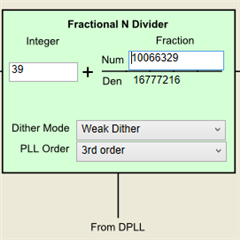

■1_EVM-DEFAULT_Select-PLL2__211220.TCS■

OUTPUT0~7 156.25MHz、带 PLL2 VCO、LMK05318的 EVM

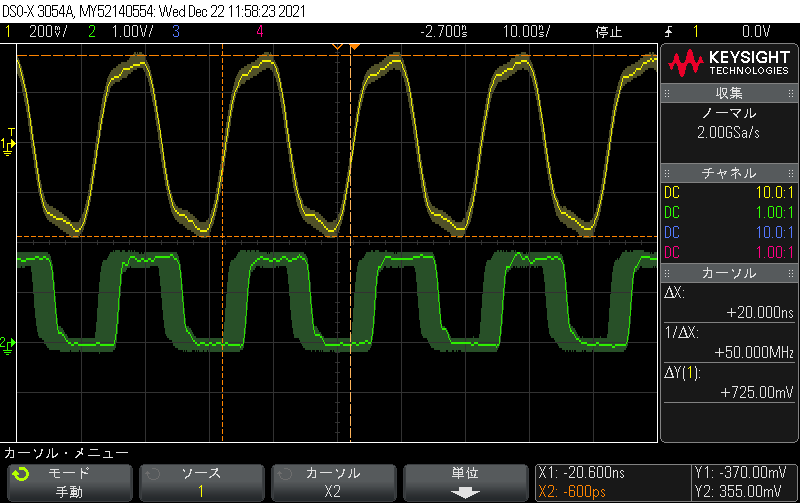

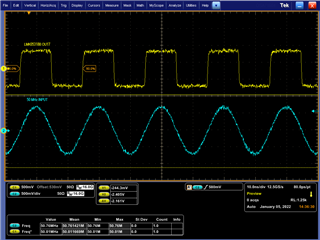

→我们得到了 SCOLE_9.bmp、似乎输入与输出同步。(确定)

(scope_9.bmp 显示多种波形。)

■2_EVM-default_out-Freq25M__211220.TCS■

OUTPUT0~7 25MHz、带 PLL1 VCO、LMK05318的 EVM

→我们得到了 SCOLE_13.bmp、似乎输入与输出同步。(确定)

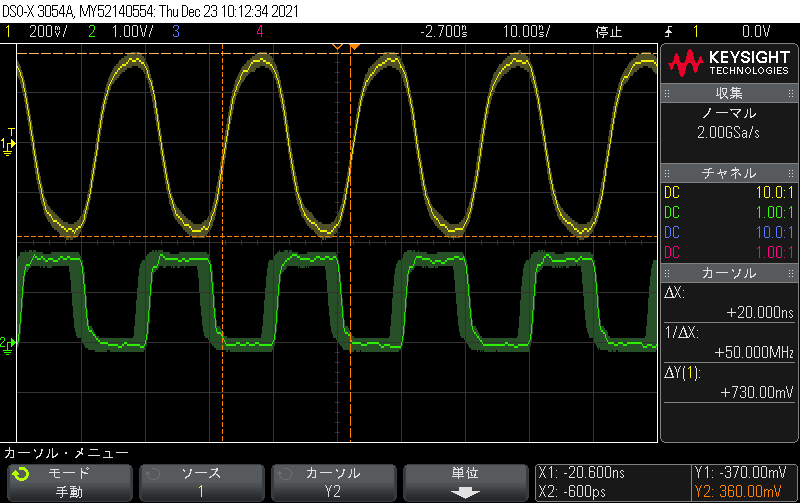

■3_EVM-default_out-Freq25M__Select-PLL2__211220.TCS■

OUTPUT0~7 25MHz、带 PLL2 VCO、LMK05318的 EVM

→我们得到了 SCOLE_14.bmp、输入似乎未与输出同步。(NG)

因此、我们不理解为什么输入与输出不同步、抖动似乎会增加。

如果您有一些建议、您能告诉我们吗?

我们假设可以使用 EVM 确认这些情况。

*在 TICSPRO 操作上,客户执行了“计算频率”->“在任何情况下运行脚本”。

e2e.ti.com/.../20211221_5F00_Scope9_2C00_-Scope13_2C00_-Scope14.pdf

e2e.ti.com/.../1_5F005F00_EVM_2D00_default_5F005F00_Select_2D00_PLL2_5F005F00_211220.tcs

e2e.ti.com/.../2_5F005F00_EVM_2D00_default_5F005F00_OUT_2D00_Freq25M_5F005F00_211220.tcs