主题中讨论的其他器件: ADS1298

工具与软件:

TI 工程师

您好!

我有以下3个问题要问:

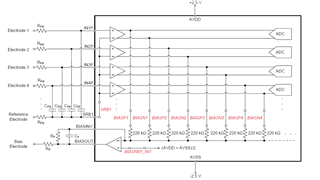

1.根据下图、我会连接 N 端作为参考。 芯片的 N 端引脚是否需要从外部连接到 AVDD?

2.用菊花链配置连接两个芯片 两个芯片上的 SRB1引脚是否需要连接在一起? 有关两个芯片之间的通道连接、请参阅问题1的示意图。

3.如果两个芯片使用第一个芯片的偏置输出来共用偏置驱动、那么第二个芯片的 Biasout 和 Biasin 引脚是否无需连接、而只有第二个芯片的 Biasin 引脚需要连接第一个芯片的 Biasin 引脚?

我很感谢您的答复!

谢谢!