主题中讨论的其他器件: UCC28740-Q1

您好:

我设计了一个参考 PMP41009的反激式转换器。 但是、电路不能正常工作。

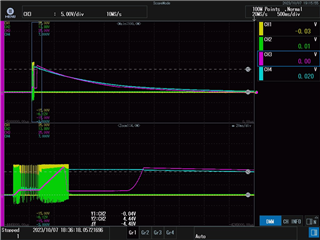

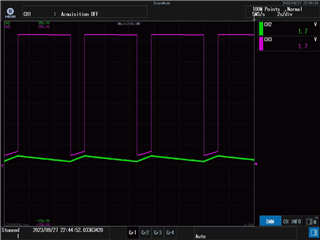

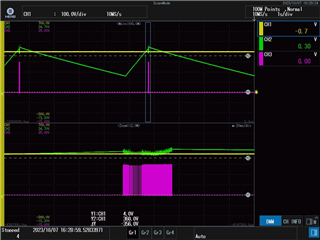

初始状态,引脚和 VDD 引脚波形如图1所示。它们的电势会在同步 μ s 中上升、此时、我可以在 VDD 电压达到导通阈值阈值时观察到三个触发脉冲。

图1:

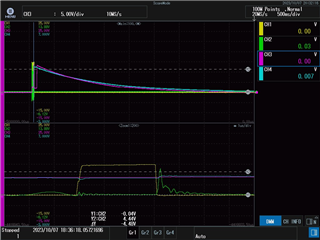

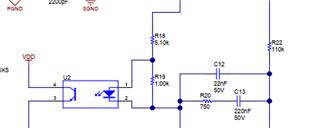

修改 RS1以降低 VIN (run)后、图2中显示了 HV 引脚和 VDD 引脚波形。上升时间期间存在电压差。 此时无法观察栅极输出。

图2:

您能告诉我哪些情况会导致这种情况吗?

非常感谢,

祝你一切顺利!

您是指将 C314更改为242nF 吗? 为什么使用750Ω 电阻器?

您是指将 C314更改为242nF 吗? 为什么使用750Ω 电阻器?