您好专家:

我使用的是 RTOS SDK 07.03和 EVM 板。

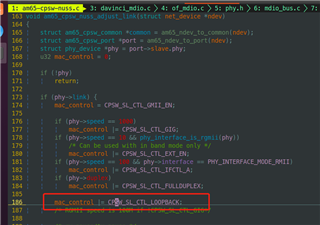

我们通过 RMII 接口连接 CPSW2G 端口1和 bcm89836 phy、并通过 MDIO C45协议配置 phy。 将 TDA4板直接连接到 PC、发现无法 ping PC。 通过 ifconifg、发现问题是由于 Mac 上没有 Rx 导致的。 设置 Mac loopback、ifconfig 仅具有 TX、无 Rx、这应该是 Mac 端的问题

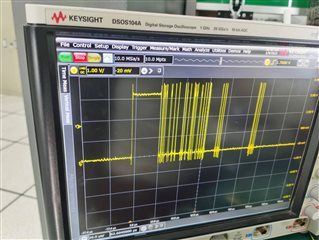

我打开了 Mac 环回、在对 PC 执行几次 ping 操作后、ifconfig 如下所示:

寄存器转储如下所示:

期待您的回复