Hi TI team:

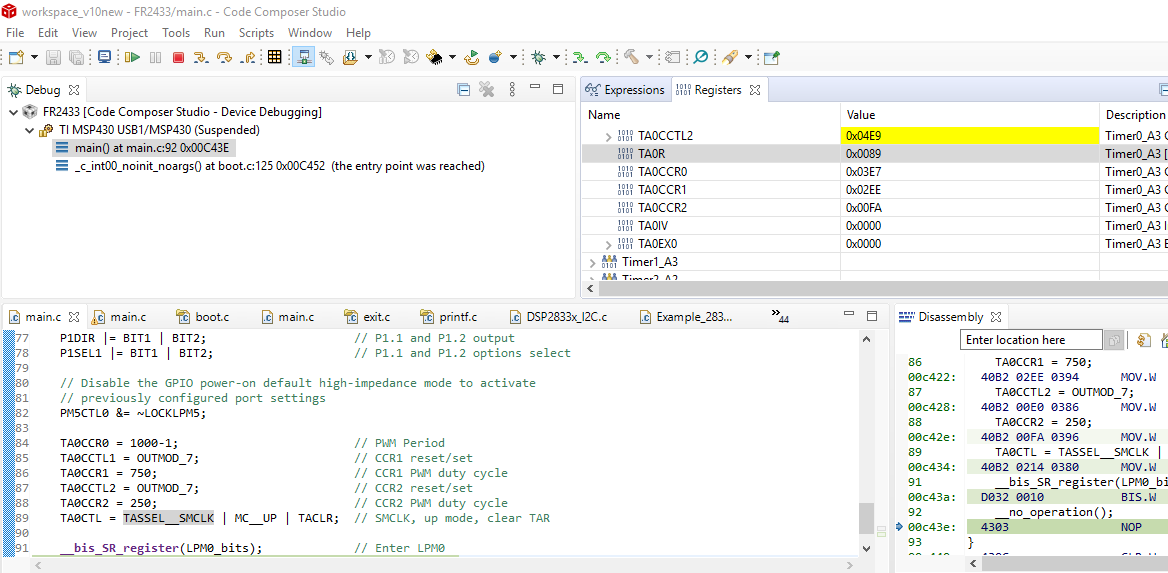

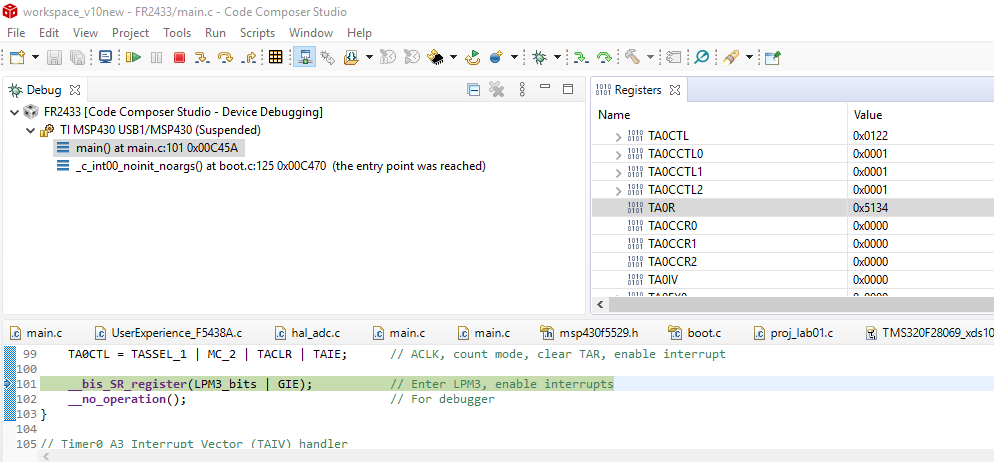

1、在使用MSP430FR2433的TA0R不计数,发现如果执行延时函数,TA0R能够正常计时,但是其他的语句无法让TA0R计时;

2、想了解下在主频配置或者定时器初始化有什么不一样的地方?现在用的是16M主频,对输入时钟进行了8分频,8s中断唤醒一次

3、又测试发现如果定时器时钟源选择ACLK只有经过延时函数定时器可以正常计时,其他语句指令不计时,时钟源选择SMCLK时,所有指令都可以正常计时。附件是测试程序。

main()

{

_DINT();

WDTCTL = WDTPW | WDTHOLD;

PortInit();

Ucs_Init_16M();

// Ucs_Init_1M();

TimerA0CounterSetup();

while(1)

{

__bis_SR_register(LPM3_bits | GIE); // Enter LPM3

WDTCTL = WDTPW | WDTCNTCL | WDTSSEL0_L | WDTIS_2;

UCA1IE |= UCRXIE;

APP_RTCPro_Delay_ms(2);

uiTranceiver=TA0R;

do

{

__bis_SR_register(LPM3_bits | GIE); // Enter LPM3

if(TA0R>=uiTranceiver)uiTemp=TA0R;

else uiTemp=TA0R+0x8000;

if((uiTemp-uiTranceiver)> T50ms) //400ms

{

P1OUT |= BIT3;

P3OUT |=BIT3;;

break;

}

}while((uiTemp-uiTranceiver)<(T200ms+T200ms));

P1OUT |= BIT3;

UCA1IE &= ~UCRXIE;

}

}

void Ucs_Init_16M(void)

{

FRCTL0 = FRCTLPW | NWAITS_1;

P2SEL0 |= BIT0 | BIT1;

do

{

CSCTL7 &= ~(XT1OFFG | DCOFFG); // Clear XT1 and DCO fault flag

SFRIFG1 &= ~OFIFG;

} while (SFRIFG1 & OFIFG); // Test oscillator fault flag

__bis_SR_register(SCG0); // disable FLL

CSCTL3 |= SELREF__XT1CLK;

CSCTL0 = 0; // clear DCO and MOD registers

CSCTL1 &= ~(DCORSEL_7); // Clear DCO frequency select bits first

CSCTL1 |= DCORSEL_5; // Set DCO = 16MHz

CSCTL2 = FLLD_0 + 487; // DCOCLKDIV = 16MHz

__delay_cycles(3);

__bic_SR_register(SCG0); // enable FLL

while(CSCTL7 & (FLLUNLOCK0 | FLLUNLOCK1)); // FLL locked

CSCTL4 = SELMS__DCOCLKDIV | SELA__XT1CLK; // MCLK=SMCLK=DCO; ACLK=XT1

PM5CTL0 &= ~LOCKLPM5;

}

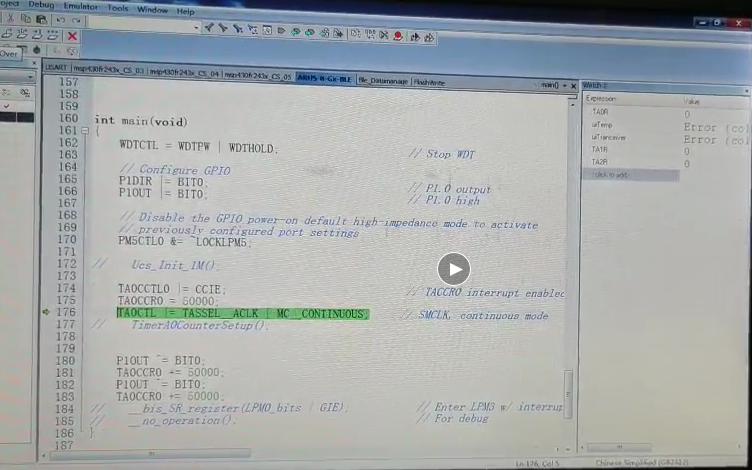

void TimerA0CounterSetup(void)

{

TA0CCTL0 |= CCIE; // CCR0 interrupt enabled

TA0CCR0 = 0x8000;

TA0CTL = TASSEL_1 | TACLR | ID_3 | MC_1; // ACLK, clear TAR,8��Ƶ��Up to CCR0

}