Other Parts Discussed in Thread: LMK04832

零延时规则要求输入时钟频率等于输出频率的最小值(GCD)。我需要进行多板同步,并且保证每次上下电时钟相位相对于参考时钟不变,所有有以下几个疑惑。

1.想问一下这里的输入时钟频率是指的是CLK_IN还是经过R分频器后的PLL1输入频率。

2.sync信号可以复位R分频器吗。

3.多板同步时,需要在Setup of SYSREF Example流程中等待外部触发信号到来之后…

为了优化相噪,LMK04832配置时钟输出时,IDL和ODL的配置一般怎么考虑,有没有统一的做法?还是说根据所研发产品的实际情况去调试,由调试结果决定是开启还是关闭改配置?

比如245.76MHz需要优化相噪一般是否开启IDL和ODL,2949.12MHz一般怎么配置IDL和ODL。如果同一颗芯片中,245.76MHz开启了IDL和ODL,那么是否有可能对2949.12MHz的时钟产生更严重的干扰。

我用了LMK04828芯片,使用osc作为输入,需要输出2500mhz时钟信号。我现在设置好了后发现芯片输出通道上没有输出。这是我的硬件资料,由于LMK04832的引脚兼容。所以这里是lmk04832的原理图。

这是我的TICS PRO配置

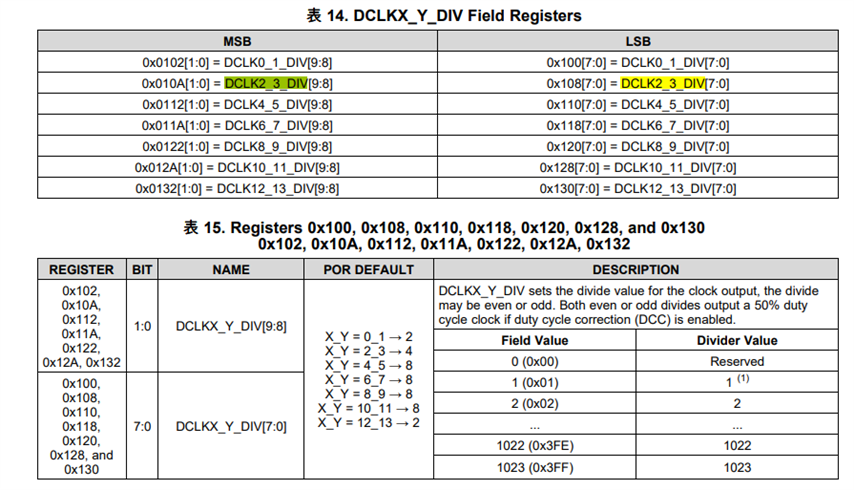

LMK04832的时钟输出例如CLKOUT2_3两对时钟全部作为DEVICE CLOCK输出时频率只能是一致的吗?之前咨询过这个问题,得到的答案是可以分别控制,今天又看了下手册,发现CLKOUT2_3的VCXO的除法器的寄存器地址是一样的,这意味着作为DEVICE CLOCK使用时只能输出一样的频率,不知道我的这个想法是否正确

LMK04832用SDCLKOUT5输出两路CMOS时钟,想要把时钟频率调到1.25GHz或者2.5GHz,发现输出时钟超过11.1GHz之后就开始衰减,调到1.25GHz时衰减已经超过10dB,切换CMOS(Norn/norm)\CMOS(norm/inv)等多种输出配置,衰减程度均不一样,可能是什么原因,手头没有评估板,没法验证。

我们想通过LMK04828SNKDREP来实现对一个输入为100MHz的LVDS时钟信号进行分配,一共设计了5路输出,全为LVDS,100MHz的时钟信号,采用Distribution模式,电路原理图如下图所示,输入的时钟信号由一个100MHz的晶振提供,从芯片的CLKin1_P/N引脚输入,原理图上的OSCin_P/N端无信号输入。随后我们通过TICS…

我采用single pll的模式配置,输入端采用的OSCIN和oscin*这个接口,配置软件采用的是TICS PRO这个,实际配置时,发现配置不了LMK04832,查看相关寄存器介绍,发现同一个寄存器,TICS PRO介绍的内容和数据手册的明显不一致,如寄存器0x0139,数据手册包含SYSREF_REQ_EN, SYNC_BYPASS, SYSREF_MUX这3个寄存器,而TICS却只有SYNC_BYPASS和SYSREF_TEMP_COMP_EN这两个寄存器…