Other Parts Discussed in Thread: ALP, , DP83640

我从贵公司购买了两块DP83640T-EVK评估板,想用来验证PTP功能,我按照 national_ALPF软件中的README_ALP.txt文档,在win XP系统上正确安装了ALPF软件与驱动;

插入两个DP83640T-EVK评估板之后,在Analog LaunchPAD界面上的左上角, Tasks -> Devices显示: ALP Nano…

我从贵公司购买了两块DP83640T-EVK评估板,想用来验证PTP功能,我按照 national_ALPF软件中的README_ALP.txt文档,在win XP系统上正确安装了ALPF软件与驱动;

插入两个DP83640T-EVK评估板之后,在Analog LaunchPAD界面上的左上角, Tasks -> Devices显示: ALP Nano…

DP83640芯片配置为100兆、全双工模式,FPGA中与之交互数据的三速以太网IP核在同时收发数据时,偶尔会报CRC错,这个错误原因是因为【该错误帧帧头中帧长度字段值(比如800)与该帧实际字节数(如21)不一致】,那么这种不一致是因为什么而导致的呢

Hi everyone,I’d like to develop IEE1588 ptp with DP83640 and ESP32、Now,my hardware has been completed,however,I have many problems during my development of the driver under the environment of ESP-IDF.The environment which I use to…

我正在使用DP83640实现1588时钟同步,我已经将PTPD协议栈移植到我的工程中,并且实现了主机和从机的时间同步,我使用主机和从机的GPIO9引脚分别输出1PPS信号,它们的相位差很大,大概有1ms左右,我尝试使用官网的C库文件EPL_v193_20091023中的ptpControl.c文件中的272~312行的代码进行相位对齐,但是并没有用,期待能够得到您的帮助。

DP83640的同步以太网模式,需要外接同步以太网芯片和锁相环电路吗?

主时钟是如何发送时码信息的,从时钟使能同步以太网模式时,它又是怎么接受时码信息的?官方有没有参考的同步以太网代码。

还是仅仅使用DP83840芯片就能实现

TI支持人员,您好:

目前我们使用DP83640PHY芯片用于在linux端实现PTP协议,在使用ptp4l软件进行测试(指令:./ptp4l -i eth0 -m -H)出现如下报错:

ptp4l[1970.968]: port 1: assuming the grand master role

ptp4l[1971.969]: timed out while polling for tx timestamp

ptp4l[1971.969]: increasing…

使用海思3559A连接的DP83640;

目前的情况是phy运行不稳定,有时候可以发现phy,有时候发现不了;

使用mdio读取phy 的寄存器,发现读取的值有时候是正确的,有时候是错误或者全FFFF;

示波器测量MDIO波形,MDC正常,MDIO无法被正确的拉低,拉低的时候,有一个固定频率的脉冲出现;(移除DP83640,运行MDIO,波形正常)

查看手册,上电时序,对MDC要求是32个clock,但是海思的MDIO是在phy上电后一直产生,这个是否有影响…

如题,芯片工作不正常,配置引脚上下拉无法生效,具体提现在测量配置引脚的电平时,明明上拉的引脚却是低电平,9个上拉电阻,只有4个正常上拉,剩下5个均为低电平(此处详见附图),且模式确实也未配置正确,本设计配置模式为RMII Master模式,PHYADDR配置为00001,因此配置COL、RX_DV、TXD3均上拉,但测量电平仅TXD3为高电平,其余两个均为低电平,且配置均未生效,求大佬解惑

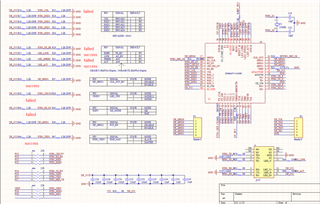

原理图部分如下:

想用STM32F4和DP83640实现1588时钟同步,之前从未有过类似额开发经历。我已经下载了snlu049的开发库,请问我需要将什么内容移植到STM32的工程中呢?我看ST官方提供的1588例程需要移植LWip和FreeRTOS,然后连接PYH以太网芯片,使用STM32自身硬件功能实现PTP同步。要是我使用DP83640这款自带1588功能的芯片,我该如何下手呢…

有一款产品在做完温循试验后出问题,查到最后发现是DP83640这个PHY芯片的PHY_PG4_PTP_EDATA寄存器读取出错导致。

我们的产品在运行过程中ARM芯片会提供一个1PPS信号给PHY,作为event输入,PHY需要读取此event的时间戳并保证和ARM本地时间同步,但是出问题的PHY芯片在读取这个1PPS event时间戳时得到的是错误的,比如我们尝试给PHY芯片写入0s时间,但是读到的1PPS时间戳为33554944s,转换为二进制是

CPU为am335x,starterware,网口芯片为dp83640,

板子接电脑时,网口可正常通信,收发数据,但是两个板子对接时,网口led-link灯不亮,

各位大神,是否知道哪里配置有误?谢谢。

各位大师:

在使用TI DP83640时, DP83640与ARM通信不上, 工作模式为RMII,晶振为25MHZ,TX_CLK&RX_CLK都是50MHZ, CLOCK OUT为25M,麻烦问下会是什么原因导致CLOCK 输出不对???

如题,看到开发板上都没有使用DP83640芯片上的JTAG口。

这个口是保留给TI的还是集成用户的?具体是用来干嘛的?能举个例子就最好了。

找了很久没有找到相关资料。发帖求教各位专家。

用到DP83640与 DM4818 RMII通讯,dp83640连接到dm8148的EMAC1,测试发现网络无法正常工作

现象描述:接上网线时RJ45的link亮,Linux可以读取到DP83640的id;用PC ping 开发板时RD0、RD1用示波器可以看到波形;ping 网关时TD0、TD1用示波器看到波形,RJ45的黄灯会闪烁,但是没有返回数据(ping失败);查看驱动的统计信息,发现接收数据为0…

DP83640用于RMII从模式时,X1脚输入50M晶振,那么是通过哪个引脚给MAC侧提供50M参考时钟呢?

各位:

现在知道一个MDIO bus 可以同时管理多个DP83640,那么一个RMII接口是否可以同时接多个PHY(DP83640)?

大侠们好,

用了一片dp83640,led模式配置为mode2,如下:

In Mode 2, LEDs are configured as follows:

LED_LINK = ON for Good Link, BLINK for Activity

LED_SPEED = ON in 100 Mb/s, OFF in 10 Mb/s

LED_ACT = ON for Collision, OFF for No …

在做一个EtherCat的板子,使用倍福的ET1100芯片,PHY用的是TI的dp83640。晶振起振,ET1100的时钟信号也输出了25MHz的时钟信号了,网线一头接板子,另一头接电脑也显示了本地连接成功,ET1100是通过网线将程序烧进去的,现在软件读不出ET1100来。就像用MDK用j-link下程序一样找不到CUP是一样的情况。现在想知道dp83640到底正常工作了没有。附件是原理图。如何去测量?

参考官方的一个demo设计的DP83640电路图,有源晶振25M,使用MII模式,上电后DP83640的RXCLK和TXCLK均无输出,有源晶振的输出正常,单片机通过MDIO和MDC去读DP83640的内部寄存器全是0xffff,不知错误在何处,附上全部电路图,麻烦专家帮我看一下,项目挺急的,已经在这卡了好久了,好心塞。想帮我看看是否电路图有问题。示波器观察晶振输出信号的峰峰值才800多毫伏,不知是否是晶振的原因?VCC是3…