芯片为LMK04828,VCO频率为2.5GHz,周期为400ps,半周期即为200ps。若设置DCLKoutX_HS = 1,指的是DCLKoutX输出时钟信号偏移0.5个VCO周期,还是说:DCLKoutX_DDLY_CNTH/L的延迟步进或单位等于1/2 VCO周期?

比如DCLKout2 = DCLKout4 = 250MHz(周期4ns),要想两个时钟的相位差为200ps,如下步骤可否实现?

(1)DCLKout2_HS = DCLKout4_HS…

芯片为LMK04828,VCO频率为2.5GHz,周期为400ps,半周期即为200ps。若设置DCLKoutX_HS = 1,指的是DCLKoutX输出时钟信号偏移0.5个VCO周期,还是说:DCLKoutX_DDLY_CNTH/L的延迟步进或单位等于1/2 VCO周期?

比如DCLKout2 = DCLKout4 = 250MHz(周期4ns),要想两个时钟的相位差为200ps,如下步骤可否实现?

(1)DCLKout2_HS = DCLKout4_HS…

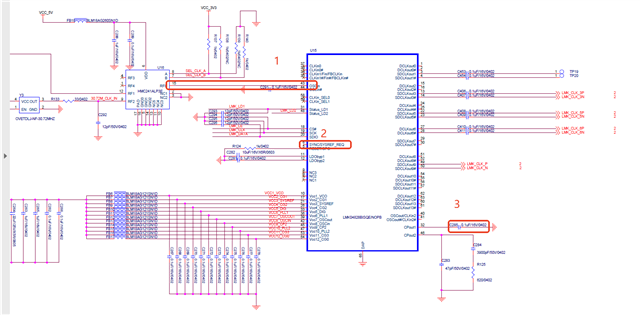

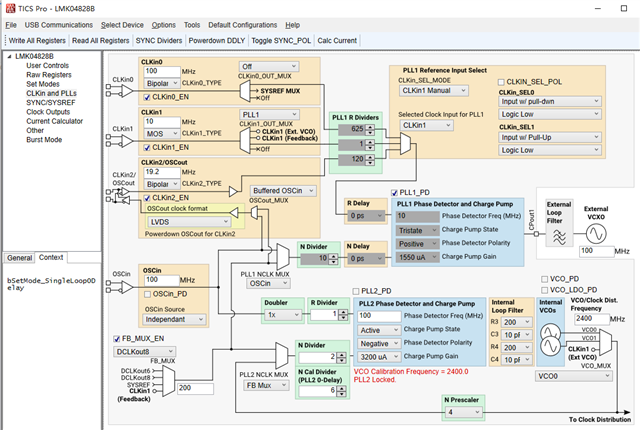

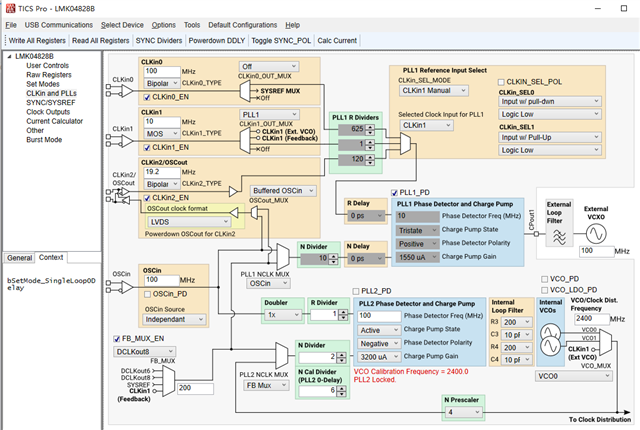

我在配置04828芯片,使用clk1作为输入,需要输出device clk 240M,sdclk输出1.875M,确定device输出时钟正常,但是sdclk输出不正确,下面是电路图和我用TICS生成的寄存器配置表,请帮我分析下原因,给我点配置上的建议。在电路上使用上下拉禁用了SYSNC/SYSREFREQ引脚。

Fullscreen12345R0 (INIT) 0x000090R0 0x000000R2 0x000200R3 0x000306R4 0x0004D0…

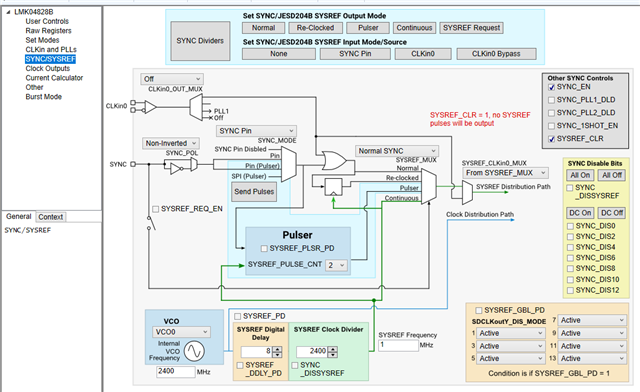

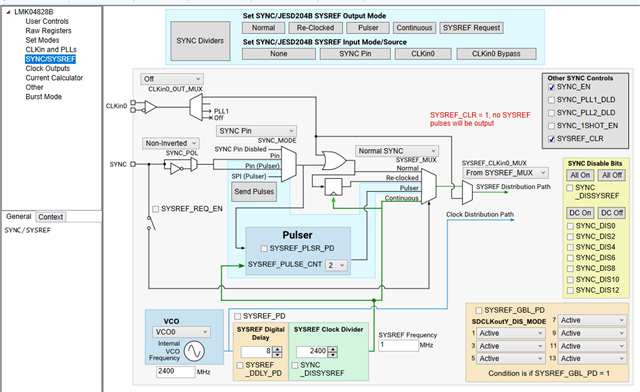

我在使用嵌套零延时这一方案时实现204B协议的要求时,发现输出时钟相对于参考时钟的抖动性较大,导致多板间多次上电存在细微的相位偏差,请问这一现象正常吗。

如果需要精确同步,需要使用分频器方案或者别的什么方案吗。

我的参考时钟和sysref是一样的,只有3.125M,输出时钟是200M。

我需要使用LMK04828产生同步时钟来同步两个板子的DAC输出(204B接口)。硬件上我们直接使用的fpga引脚和sync直连。

目前遇到了如下问题:

按照配置TI软件的寄存器设置进行了嵌套零延时模式(nested zero-delay dual-loop mode)的设置,并且按照Setup of SYSREF Example的流程进行了分频器的复位。

我用两种同步方案进行了尝试,(sync_mode = 2 , SYSREF_MUX = 2)设置和…

请教LMX2594使用方法,输入156.25Mhz,输出2个5GHz时钟给ADC12DJ5200使用,帮忙看下原理图是否有问题,TICS pro生成的工程文件对吗?

您好TI工程师,我最近在调试我们的一款时钟芯片04828,但是对芯片的相关进行配置后发现PPL1和PPL2均无法锁定

硬件电路图:

1、在硬件上尝试做了下面修改采用FREF_RX_IN 输入10Mhz时钟。

2、增加了SYNC/SYSREF_REQ控制信号,使用控制芯片在完成配置后设置为高电平后写寄存器0x0144 0XFF

3、去掉了CPout1的电容使其悬空。

软件配置:

寄存器文件如下:

…现在使用相同的寄存器参数,每配置一次,输出频率就发送一次变化,实际输出频率会在设定频率附近变化,但是每次都不一样,有时候与设定值很接近,有时候偏差很大。寄存器参数如下,写寄存器的顺序也是按照下表逐个写入的。麻烦问一下这是什么问题,是寄存器配置参数问题,还是写寄存流程有问题,还是硬件问题?

R0 (INIT) 0x000090

R0 0x000000

R2 0x000200

R256 0x01001E

R257 0x010100

R258 0x010200

R259

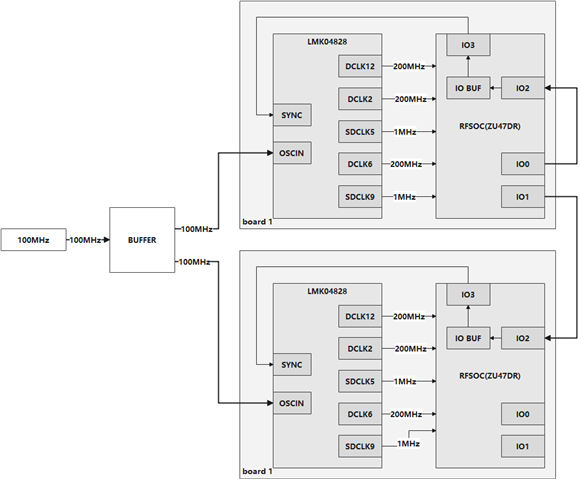

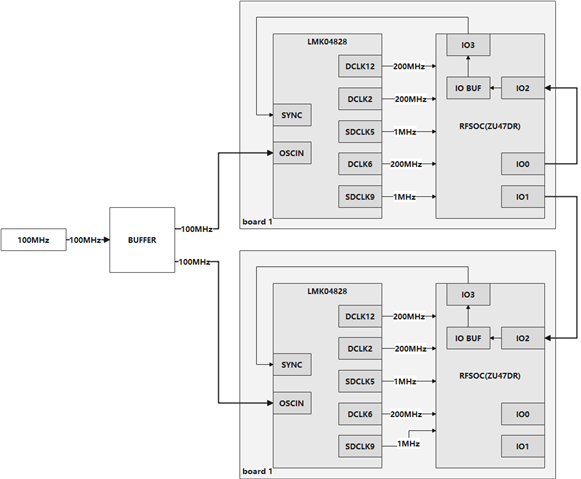

我有两块RFSOC(ZU47DR)板卡,时钟芯片使用LMK04828,想要实现两块板卡的采样同步。根据现有的设备,构建如下图所示时钟网络,经过尝试,两块板的ADC采样并不是同步的。请问是硬件时钟结构有问题还是我软件配置有问题?

两块板卡的LMK04828配置如下:

SYSREF生成流程参照数据手册9.3.2.1.1

RFSOC多片同步参考RFSOC手册PG269中MTS Sequencing下给出的流程, use case 2

我有两块RFSOC(ZU47DR)板卡,时钟芯片使用LMK04828,想要实现两块板卡的采样同步。根据现有的设备,构建如下图所示时钟网络,经过尝试,两块板的ADC采样并不是同步的。请问是硬件时钟结构有问题还是我软件配置有问题?

两块板卡的LMK04828配置如下:

SYSREF生成流程参照数据手册9.3.2.1.1

RFSOC多片同步参考RFSOC手册PG269中MTS Sequencing下给出的流程, use case 2

配置参数

24'h0000_80

24'h0002_00

24'h0100_08

24'h0101_00

24'h0102_00

24'h0103_00

24'h0104_20

24'h0105_00

24'h0106_F0

24'h0107_17

24'h0108_08

24'h0109_00

24'h010A_00

24'h010B_00

24'h010C_00…

我们使用fpga通过 spi (3线)控制 lmk04802,中间通过 TXB0104RGY这款转换芯片进行电平转换。lmk的reset引脚外接fpga 的io,可以设置成input/output/高阻。

目前测到的现象是,上电之后,供电正常,clk0有100mhz时钟,Status_LD2为低,Status_LD1为低。

通过fpga发送任意读写spi的指令,Status_LD1变为高。

fpga读lmk 的默认值读到的数据如下:全0或全1

8003…

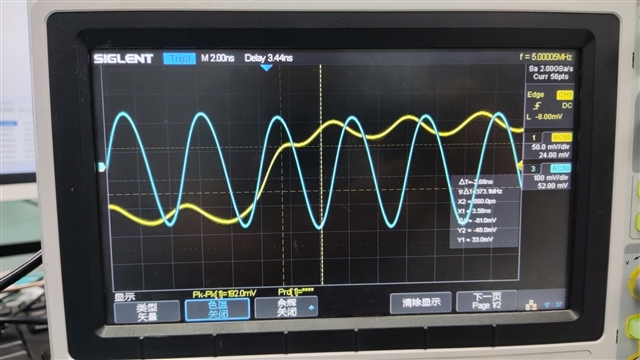

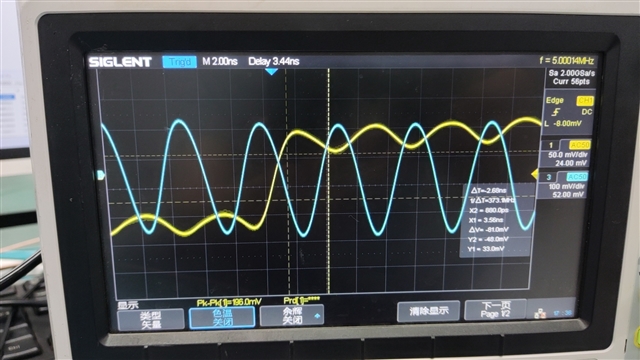

LMK04828输出的200M DCLK和5M的SDCLK每次配置后相位都会发生改变,见下图

,输人时钟是800M,直接分频,没有使用锁相环,这是寄存器配置,

,输人时钟是800M,直接分频,没有使用锁相环,这是寄存器配置,

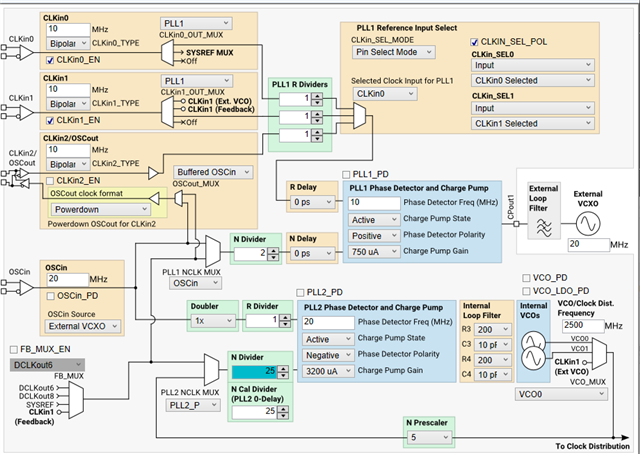

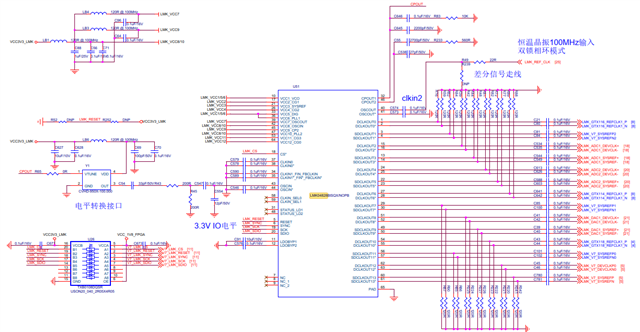

背景:

1,LMK04828使用两个pll,外部100m恒温晶振从clk2输入,pll1从CPOUT1和CPOUT2输出100m时钟,然后再经过外部压控振荡器后从OSCIN输入,电路如下图:

2,LMK04828寄存器配置如下:

R0 (INIT) 0x000090

R0 0x000080

R2 0x000200

R3 0x000300

R4 0x000400

R5 0x000500

R6 0x000600

R12 0x000C00

R13 0x000D00

R256…

TI的工程师:

您好,请教个问题:

信号处理板上使用了LMK04828时钟芯片,输入10MHz时钟信号,输出122.88MHz时钟信号,这种非整数倍输出,目前测试输出时钟信号相位噪声很差,但输入30.72MHz,输出122.88MHz 这种整数倍输出,信号噪声就很好,请问LMK04828是否不支持这种非整数呗配置?如果支持,需要怎么配置?谢谢!

你好!

我们目前使用的lmk04828芯片,芯片在正常工作的情况下RESET/GPO管脚是高电平还是低电平?

我们外部是否需要对此RESET/GPO管脚控制。

RESET/GPO管脚仅作为复位管脚。无其他复用功能

你好,TI工程师:

我们最近在使用LMK04828芯片的时候遇见了这样的问题:

使用场景,使用了控制芯片为zynq 7045 的SPI xai ip做的控制,使用SPI四线模式来完成读写,使用管脚(MISO)为'Status_LD1'。

问题如下:

1、这里再硬件设计的时候该引脚(Status_LD1)是否需要外接高电平。

2、如何将该引脚配置为高电平(具体的寄存器设置)。

3、是否有管脚能确定该芯片的工作状态…