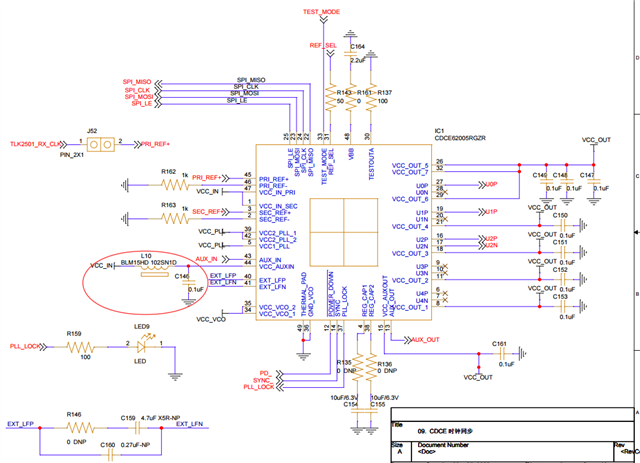

按照默认配置进行配置之后,时钟没有输出,

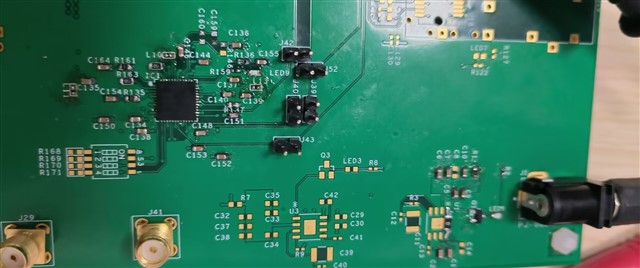

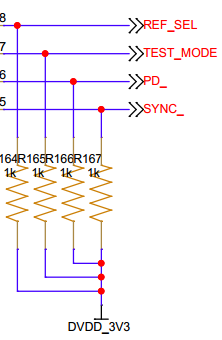

采用的是sec_ref作为参考时钟,但是sec_ref引脚的电平总是为0.8V,#SYNC #POWER_DOWN 强制上拉为高电平,REF_SEL下拉为低电平,其余电路均按照官网上DAC348X评估板进行设计

对寄存器的配置为

parameter ram0 = 32'h81840320;

parameter ram1 = 32'h81840301;

parameter ram2 = 32'h81…

按照默认配置进行配置之后,时钟没有输出,

采用的是sec_ref作为参考时钟,但是sec_ref引脚的电平总是为0.8V,#SYNC #POWER_DOWN 强制上拉为高电平,REF_SEL下拉为低电平,其余电路均按照官网上DAC348X评估板进行设计

对寄存器的配置为

parameter ram0 = 32'h81840320;

parameter ram1 = 32'h81840301;

parameter ram2 = 32'h81…

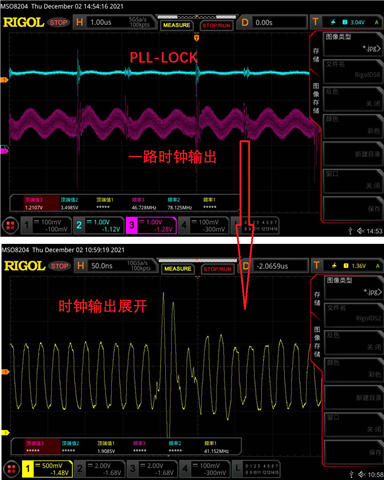

我的CDCE62005能够正常配置和输出,但掉电后再重新上电,PLL_LOCK会变成锯齿状,不是稳定高电平了,输出频率也会不准确。

这时我需要重新手动对VCO做校准才会恢复正常。但一旦掉电再上电又会失锁。

这是什么原因呢?

期待您的指点!

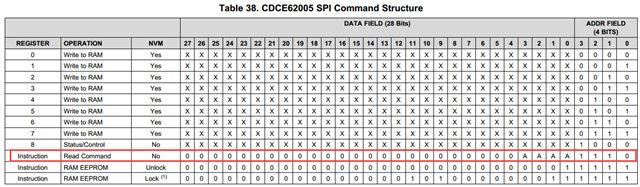

很希望能请教一下CDCE62005的读取寄存器命令应当怎样写。

根据芯片手册,当我想要读寄存器1,我应当用MOSI发送“E1_00_00_00”对吗?

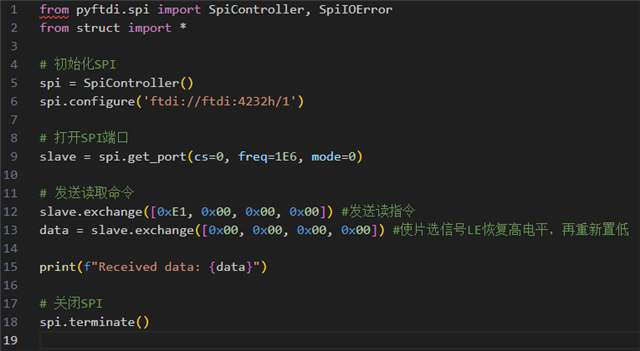

我使用ft4232h的python库——pyftdi编写了程序如下:(可以看12和13行)

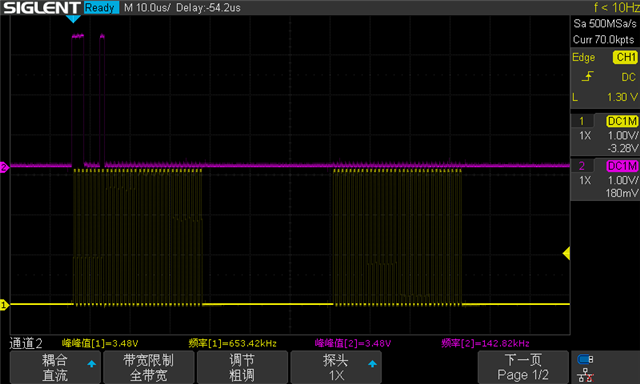

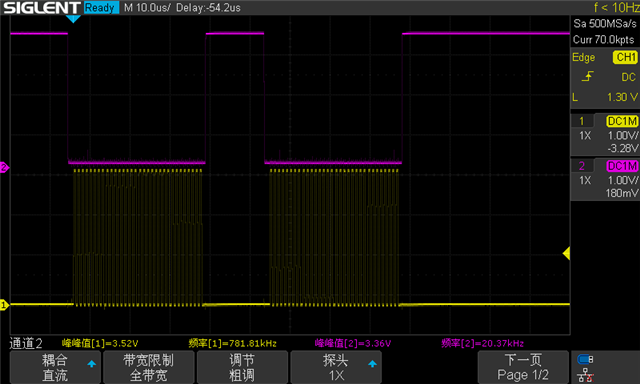

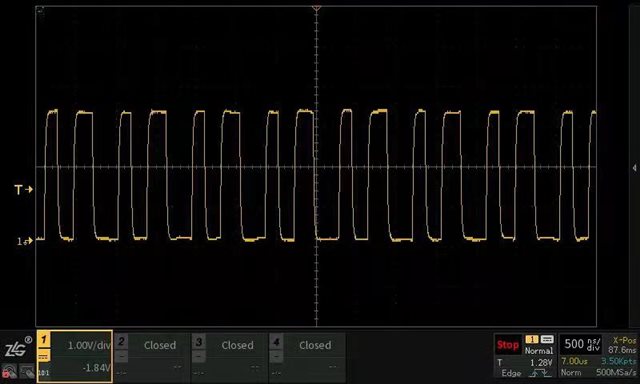

用示波器抓取CLK和MOSI的时序为:

LE(片选)为:

MISO的时序为:(什么都没读到)

我的SPI时序有错误吗?还是读指令不正确?

另外还有一个异常情况…

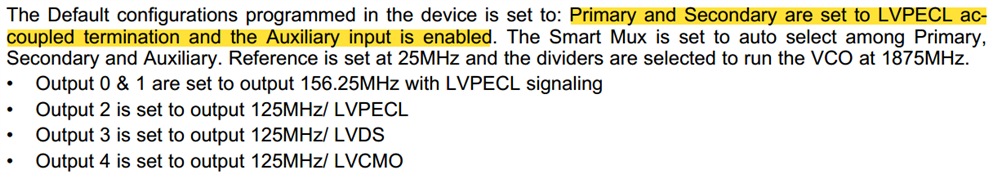

我注意到芯片的默认工作情况为下图所示:

我现在使用AUX_IN输入25MHz单端时钟(方波 2Vpp 无偏置 HiZ)

此时PLL_LOCK为持续高电平——PLL成功锁定,且U3和U4有正确频率的波形,但U0、U1、U2只有直流偏置却没有输出时钟波形,请问这可能是什么原因呢?

另外,U3和U4的输出偏置电压为1.6V,正常吗?我使用的输入时钟应不应该设置偏置?

【补充说明:】

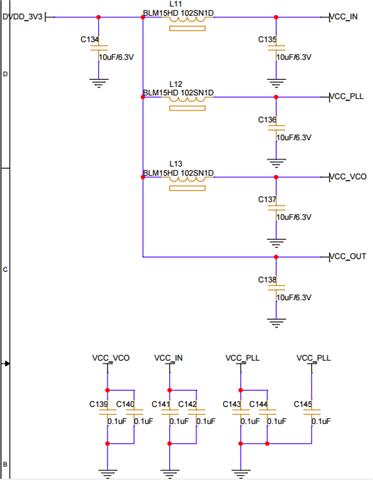

实测整个芯片的各个VCC引脚均供电正常,VBB

…我按照芯片手册里的参考电路绘制了电源:

图中的4个电感我依照型号使用了1000ohm的贴片电感;电源由外部台式稳压电源提供3.3V直流电;

但出现问题:

期盼您的指点!

采用AUX_IN输入25MHz时钟,外部配置引脚如图均设为高电平(经测量确为高电平),芯片寄存器为默认,希望能实现芯片手册示例中的输出(156.25MHz和125MHz等输出)。

经测量芯片供电正常,输入时钟正确给入,但都无输出,且PLL_LOCK始终为低电平。求问可能是出了什么问题?

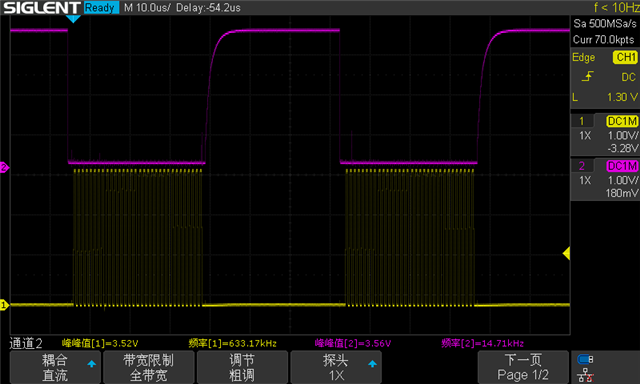

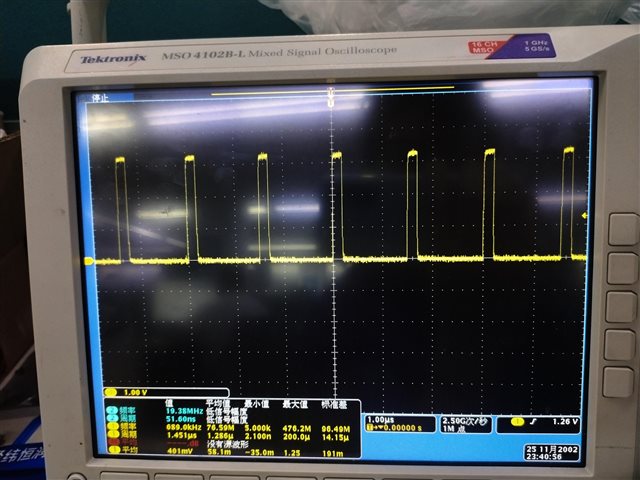

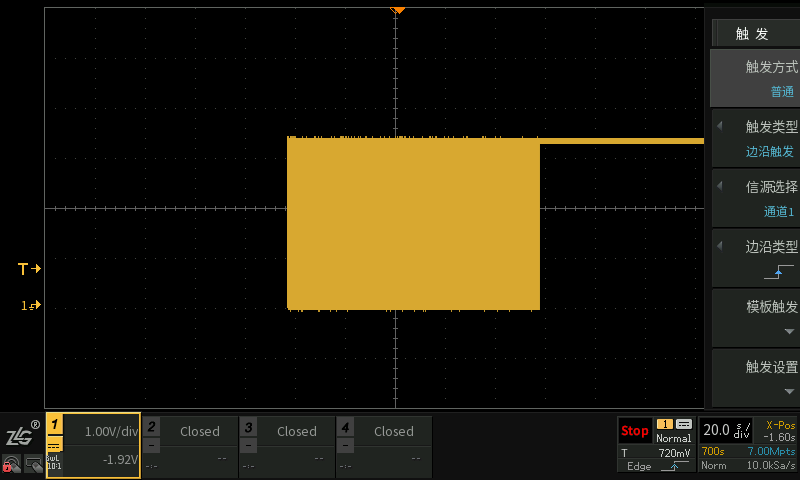

输入时钟为40M,在使用EVM配置输出单通道100M时,实测的输出频率为103.7M,LOCK引脚输出为方波,请问这有可能是哪些方面会有问题,下图为lock引脚的输出波形,谢谢

你好,我想用我自己的电路初始化和编程CDCE62005。但是现在我有一些问题。

首先,我不确定构建的芯片外围电路是否正确,我无法确认芯片是否工作,也没有办法在芯片手册中验证芯片的正常运行。请帮我检查一下我的电源电路是否正确,引脚配置是否正确。

其次,在芯片上电后,我去读寄存器8,返回的数据都是零。我使用模式0的spi时序,/power_down引脚和/sync引脚悬空,但我测量它们的功率电平是逻辑0。

根据数据表,芯片上电(vcc给入后,无需拉高拉低power_down引脚…

您好:

我们遇到两片CDCE62005级联后,部分板卡第二级芯片Lock信号失锁问题。

我们的芯片电路是完全参考TI官方6678开发板的,配置的SPI接口由FPGA控制,配置文件由官方软件生成;

已经生产过多批板卡,但从去年开始出现故障,去年累计2例,今年到目前为止又出现7例!

失锁故障都仅仅发生在第二级;对一块故障板卡的前后级芯片进行对调,失锁故障还是发生在第二级。

对调实验排除了芯片问题,非新板卡排除了硬件问题和软件问题,对调实验及非整批板卡出问题排除了焊接问题…

数据手册显示fan-out mode时,CDCE62005可以输出最大1.5GHz?想咨询下,如果需要输出1.25GHz的频率,是否需要输入1.25GHz的时钟?

您好,关于时钟芯片最近遇到三片CDCE62005异常,如以下内容。请进行解答,谢谢。

1、遇到两片该芯片输出PLL_LOCK一直处于失锁状态,如下图PLL的输出信号;

进行测试,将完全失锁的芯片焊接在另外的位置,故障现象不同,如下图所示

2、另外一片需要1分钟多才能PLL-lock信号才能正常,如下图所示PLL-lock波形;

Hello, I want to program CDCE62005 by myself through SPI, but everytime when I set SPI_LE to HIGH and do rising edge to Power_Down, I just hava 20ms to access device registers, but I need to do 「Copy RAM to EEPROM – Unlock」 it have…