Other Parts Discussed in Thread: CDCE62005

上图是我的硬件原理图设计。

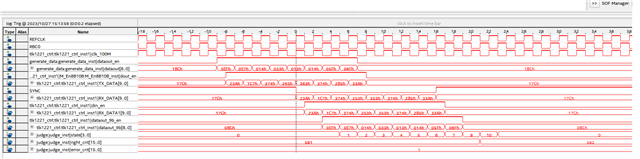

使用FPGA程序驱动TLK1221芯片,RBCOMDE=1,REFCLK=100MHz。

我写了一组测试数据,原码为EF E7 14 33 13 14 5F 6F,将它通过编码模块,编码为23A 1C7 374 253 353 374 2B5 33A。编码后的数据输入到TLK1221管脚TD0--TD9。在上图JP4接插件中,我将TXP,TXN分别接到RXP…

各位论坛里的高手:

大家好!

公司最近一个项目上用到了CDCE62005这个芯片,在调试的过程中遇到了PLL不能正常锁定的情况。

板子上CDCE62005的原理框图如下:

参考时钟是来自于别的模块,在调试过程中暂时用信号发生器来代替了。

我的调试过程大概如下:

1、我自己的板子上实际的输入和输出设置如下:

环路滤波器的设置如下:

软件生成的寄存器值如下…

我用TI的62005EVM的SPI口给62005烧写寄存器,烧写到eeprom中,有时上电5路输出都正常,有时上电第一路没有输出,其他4路工作正常,后来发现输出不正常是第一路ram中的寄存器的值全是0,也就是从eeprom中读寄存器值到ram时,第一路读错了,其他4路都正确,请TI员工和技术高手帮忙分析一下,着急啊

自己设计的6678原理图,FPGA+DSP6678,FPGA控制6678上电,DSP时钟由2级CDCE62005提供,第一级由外接参考时钟25M晶体提供;第二级由第一级产生100M做参考,大体原理是参考开发板设计,相关电路也是采用开发板设计,PD是一上电就拉高。通过软件工具和手册配置了两级62005寄存器输出100M,现象是所有输出均没有,PLL_LOCK长低;经测量电源均正常;

1

…大家好,我的设计是参考tms320c6678电路设计的,原理图一样。

现在的问题是,输入为AUX 25Mhz无源晶振,我用示波器*10档测量晶振的情况是,探头刚碰到晶振,晶振就不振了,但是用示波器单次触发可以看见,探头碰到晶振角上的瞬间是在震动的,频率为25Mhz没错,请问这算是正常起振状态吗?

第二,我按照6678的FPGA代码配置cdce62005,配置没有问题,PLL_LOCK引脚置高…

如题,需要的本来是100MHZ,实测单端有-8dbm,但是300MHZ也有-13左右

请问谁有FPGA通过SPI配置CDCE62005的代码工程,我门的芯片的时钟一直配置不出来,向大家求助了

大家好:

最近新焊接了一批6678的板卡,发现JTAG无法连接,后来发现是时钟没有锁住,前几次上电还可以锁住,之后再上电就无法锁住,lock信号波形是600KHz左右的脉冲。

时钟部分参考的EVM板,使用的是cdce62005,100MHz输入,输出156.25MHz、100MHz和62.5MHz。SPI读写时序是用FPGA做的,一样的时序,一样的配置文件,在老批次板卡里是好的。

后来检查配置文件…

我们在做一个设计,用到cdce62005,输出时钟是155.52,输出也是155.52,用cdce来做时钟clean,我在配置cdce62005的时候,想把环路带宽设置成100hz,但是ratio pole T3 to T1这个选项设置总是出问题,一直显示是 1,

请帮忙看看是什么问题,谢谢

cdce62005的晶体不起振,求助! 确认为3.3V没问题,晶体的电容焊了47pf,后来又拆了,都不起振!

我们参考6678 EVM做的一款带有两个DSP的开发板,上电控制用spartan6。两个DSP分别用了参考EVM板的两组CDCE62005时钟芯片。

今天我在调试DSP1的时候出现了Error connecting to the target:Connect to PRSC failed的问题,然后就去测时钟,发现DSP1时钟芯片的输出波形都不正常,但是DSP2的CDECE时钟芯片的输出时钟完全正常!

我测了时钟晶振…

大家好,我正在调CDCE62005遇到了一些问题,忘大家不吝赐教

我的板子上用了一片CDCE62005,只有25MHz的晶体输入。我想获得一路100MHz、一路66.67MHz的LVDS时钟输出。

遇到的问题如下:

1. 由于CDCE62005内部有默认的寄存器值,我直接发SPI写寄存器5,将输入改成Aux IN,即25MHz的晶体输入。结果发现CDCE62005的每一路都有时钟输出…

最近组里项目需要用到CDCE62005这个时钟芯片,电路是前面师兄画的只能通过SPI接口配置,用的是网上的clk fpg感觉总是配置不上,输入是25MHZ晶振,需要2,3,4输出端只有4有135MHZ的时钟输出。2.3端口只有2.7V左右电平无时钟,然后用另一块没配置过的芯片也是一样的输出结果,因为是新手不知道是哪里出了问题,希望大神们帮我想想办法,谢谢了。

时钟输入:

采用单端从PRIREF+输入10Mhz,PRIREF-接1K电阻接地

测试1:

Output4输出选择不经过内部VCO的LVCMOS时钟,输出是10Mhz,频率值正常,

请问:这是否可以说明外围电路供电和配置是正常的,并且Input Buffer 设置(PRI Buffer VBB,PRI Buffer Termination,input Buffer select ,AC/DC termination 等)是正确的,如果不是,在单端输入(10Mhz ,VPP=3.3V,从PRIREF…

设计介绍:

我是参考6678评估板进行的时钟设计,将CDCE62005两级串联,第一级25M晶振输入,+/-50ppm精度,输出依次为66.67M、100M、66.67M、100M、100M,同时将第二路输出的100M接入第二级62005的PRI输入端,AC耦合,输出4路156.25M,最后一路关闭。

两级的PFD均为3.125M,CP CURRENT均为2mA,输出均为LVDS。

问题描述:

…

在给CDCE62005通过SPI设置到ram时,寄存器0的write read都正常,U0P/N管脚输出正常

然后使用ram 到eeprom命令后,

复位62005,通过将POWER_DOWN管脚拉低再拉高实现

再去读寄存器0的值时发现有两块板的值变为1了,还有一块板是0

其他值都写进eeprom,就只有寄存器0未写入到eeprom

请问这是什么问题?跟硬件外围有关吗?

各位大神,您好,

用两片CDCE62005给一片6678提供时钟,第一片输入为无源晶振产生的25MHZ信号,输出为两路100MHZ和一路66.67MHZ的时钟,第二片输入为第一片的100MHZ,输出为312.5MHZ时钟,现在就是第一片PLL_LOCK为脉冲形式,第二片就根本不锁定,两片时钟芯片寄存器的值分别为:

第一片:

REG0 = 32'hEB840320 ,

REG1 = 32'h68020301…

在调试CDCE62005的时候,之前因为时序问题造成了EEPROM的锁死。

具体表现为:Register 7的26位(EPLOCK)读取为‘1’;且使用RAM EEPROM unlock指令将RAM中的数据存入EEPROM失败。

请问有什么办法能够给EEPROM解锁么?从软件或硬件上?

您好!

板子上用到了3个CDCE62005,其中两个一直能稳定工作,第三个输出无法锁定,pll_lock一直是脉冲波形,输入AUX_in 25M,输出只有了第5路,125M,配置参数如下:

cdce62005_cfg_data[0] <=32'h68860320;

cdce62005_cfg_data[1] <=32'h68060301;

cdce62005_cfg_data…