Other Parts Discussed in Thread: TMDS181

Hi:

When using the TMDS1204 chip, we encountered issues with FPGA reception while receiving HDMI 2.0 signals, which may be caused by input clock random jitter. This could potentially be due…

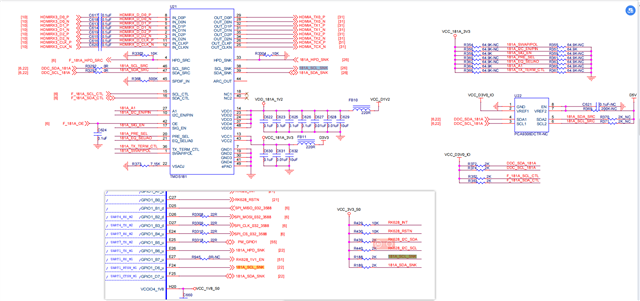

下图是我司的TMDS原理图设计,方案是由FPGA输入HDMI经过TMDS,再到RK3588,目前遇到的问题是,FPGA由输出HDMI信号,但是TMDS并没信号输出到RK3588,请帮忙分析一下我司的原理图是否设计有缺陷或遗漏,RK配置上是否有什么需要注意的?

现象描述:分辨率为4K@60hz时,画面显示黑屏,而EDID已经读取完成,但将DDC通道由监听模式改为经TMDS181处理后,画面显示正常

问题:DDC信号上除了EDID信息之外,会包含哪些和TMDS信号相关的信息,有什么工具可以将TMDS181寄存器全部抓出来?

我们主要进行了以下操作:

1、上电后,对TMDS181前8个寄存器进行read操作,能正确读出“TMDS181”对应的ASCII码;

2、继续read操作,读出的是地址08H后面的寄存器数据;

3、执行write寄存器操作,再次read操作,出现未知的值(03H),寄存器地址无法回到00H;

请问寄存器地址如何回到初始地址或者指定地址?如何验证是否正确的执行写寄存器操作?

芯片硬件配置如下:引脚IIC_EN/PIN、TX_TERM_CTL拉高,VSADJ引脚接6.98K电阻接地,SDA_SRC/SCL_SRC接地;上电后,IIC不做配置,输入1080p30,视频正常输出;通过SDA_CTL/SCL_CTL向TMDS181寄存器0x0A配置为0xE3、0x0B配置为0x1B;输入1080p60、4K30色彩不对。

咨询一下,在1080p60、4K30、4K60输入下,0x0A配置为0xE3、0x0B配置为0x1B,是否正确?是否还需要配置其他寄存器…

链接关系:HDMI 线 → 连接器 → DS125MB203 → FPGA RX

目前问题是HDMI2.1 DDC通道已经通了,但FPGA抓取不到DS125MB203过来的视频信号,读到的都是无效数据。

附件是原理图和pcb,希望能帮忙排查一下硬件设计问题,谢谢

Hi TI Team,

目前我们遇到了TMDS181视频无输出的问题,附件是TMDS181的原理图。

我们的设计是FPGA --> TMDS181 --> HDMI Connector,使用TMDS181配置为I2C模式。寄存器配了0x09值为0x02,0x0A值为0x32,其他寄存器都为默认值,视频无输出,读取出来的寄存器0x20的值为0x8A(bit7=1,power down模式),问题:

1. TMDS181是否支持这种应用…

我们的设计是FPGA --> TMDS181 --> HDMI Connector,使用TMDS181配置为I2C模式。寄存器配了0x09值为0x02,0x0A值为0x32,其他寄存器都为默认值,视频无输出,读取出来的寄存器0x20的值为0x8A(bit7=1,power down模式),问题:

1. TMDS181是否支持这种应用?

2. FPGA到TMDS181中间有0.1uf电容,TMDS181到HDMI Connector直接连接,这样的链路是否有问题…

1、两个181芯片采用pin strap模式时,HDMI接口可以link up

pin1 NC

pin10 62k电阻下拉

pin17 62k下拉

pin21和pin27 NC

pin42 上拉

2、将 FPGA to TMDS181的这个芯片配置成i2C模式,TMDS181 TO FPGA的TMDS181保留pin strap 模式,i2c配置寄存器如附件所示,这样的环境搭建

HDMI接口不通。

问题:

a、这个问题应该如何分析,是i2c寄存器配置问题,还是硬件设计问题提?

b、FPGA TO TMDS181方向信号链路采用DC耦合…