Other Parts Discussed in Thread: C2000WARE

请问一下这块板子的原理图在哪里啊,没有找到

请问一下这块板子的原理图在哪里啊,没有找到

在調試TI28379D的BOOT下載引導時,發現帶仿真器復位能透過BOOT程式指定位址運行到APP上,但是不連著模擬器,就會在BOOT跳轉位址時死掉。

C28xx:连接到目标时出错:(错误 -233 @ 0x0)JTAG IR 和 DR 扫描路径无法循环位,它们可能已损坏。尝试扫描 JTAG 扫描路径失败。目标的 JTAG 扫描路径似乎因 stuck-at-one 或 stuck-at-zero 错误而中断。(仿真包 9.5.0.00143)

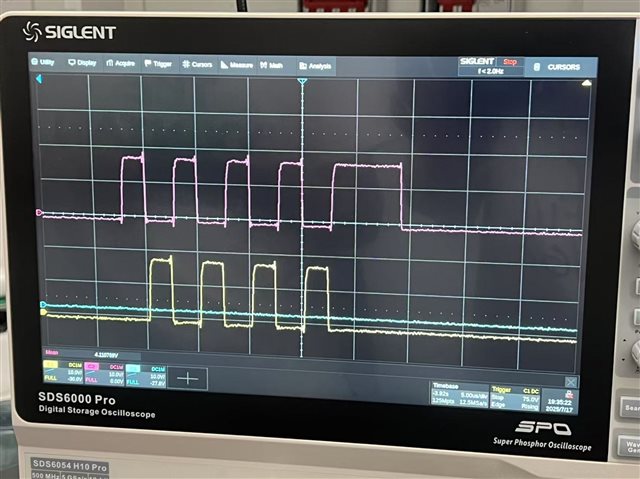

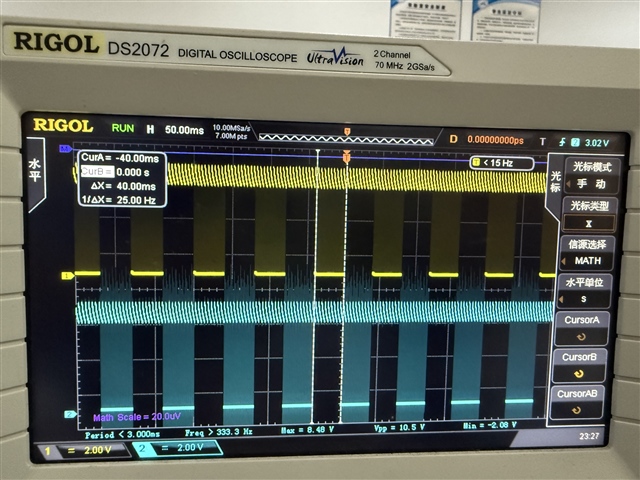

我利用eCAP的APWM模式路由到EPWM的TZ模块使之在某些条件下打嗝,但是仔细观察打嗝的波形发现,EPWM的A管和B管总是出现最后一个波形延时关断,且这个问题在EPWMA或者B随机出现,且每次打嗝都只出现在有一个管子上,这是为什么?

如图为EPWMxA和EPWMxB打嗝过程中的波形图

故障详情:

**** Build of configuration F2837x_RAM for project gridConnectedInverterLCLFltr ****

"C:\\ti\\ccs1260\\ccs\\utils\\bin\\gmake" -k all

Building file: "../F2837xD_CodeStartBranch…

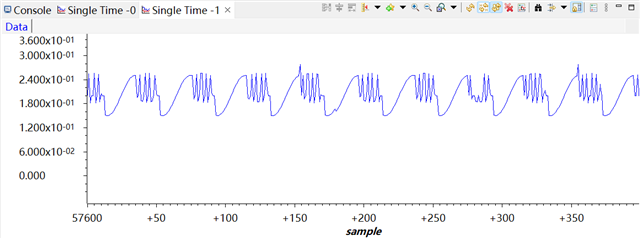

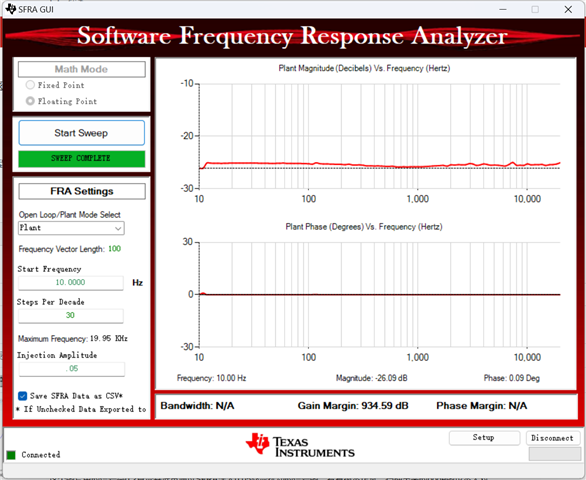

这个图片里的信号是0.2直流基准再通过SFRA注入0.05交流扰动的信号图,看着很不正常,扫描出来的bode图也不太对。

怀疑是扰动信号的问题,请问这个信号正常吗?不正常的话,可能是什么原因造成的?感谢!

我在查阅28054F该芯片的手册中发现,Tim1中断不在中断向量表中,不受PIE控制,发生中断时直接发送到CPU,那我同时使用Tim1中断和ADC主主中断时,Tim1是否会影响ADC中断的及时响应

在程序中写了DELAY_US()函数,运行之后就会跳转到ILLEGAL_ISR中断,出不来

interrupt void ILLEGAL_ISR(void) // 非法作 TRAP

{

// 在此处插入 ISR 代码

接下来的两行调试仅用于在此处停止处理器

// 插入 ISR 代码

后删除 asm(“ESTOP0”);i2c_cpld (2).zip

for(;;);

}

if (toggle == 0) { // EPWM3、5配置为50%占空比,EPWM4、6配置为高电平 EPWM_setDeadBandDelayMode(EPWM3_BASE, EPWM_DB_RED, true); EPWM_setDeadBandDelayMode(EPWM3_BASE, EPWM_DB_FED, true…

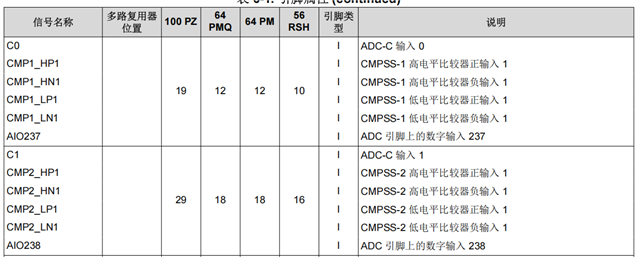

您好!我在试图用当前设备配置CMPSS,以触发epwm的TZ保护,但始终无法成功触发。

触发CMPSS比较器的外部引脚为C0:

我只需要配置高触发,也就是当引脚采集电压高于设定值时触发TZ保护。CMPSS相关的宏定义如下:

#define PVA_VDS_CMPSS_BASE CMPSS1_BASE //C0 #define PVA_VDS_CMPSS_ASYSCTRL_CMPHPMUX…

您好!

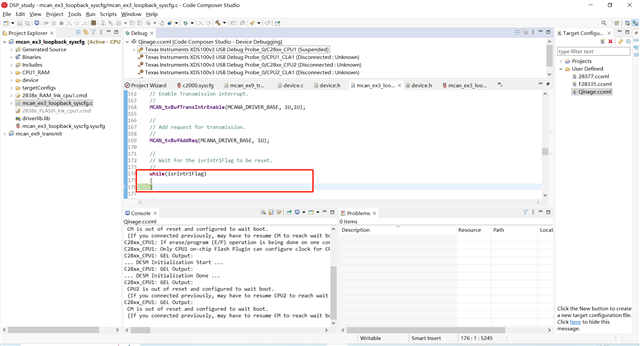

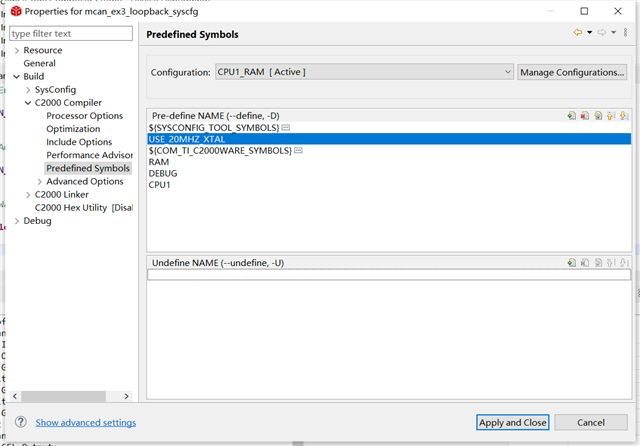

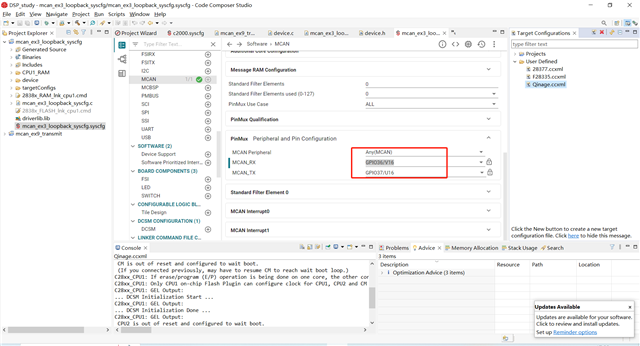

我正在使用TMS320F28388D的CANFD通信代码,我在使用官方提供的代码时发现问题如下:

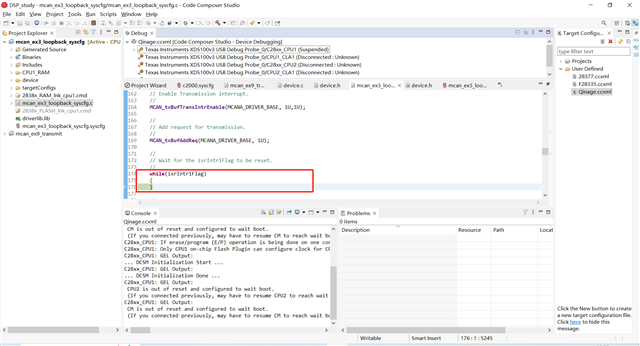

我使用的例程是MCAN_ex3_loopback_syscfg;在下载程序后进行仿真发现代码卡在while循环里面:

具体位置如下:

在这个例程中我只修改了我的晶振时钟和引脚,由25MHz变为了20Mhz,引脚由原本的GPIO30,31改为了GPIO36,37,使用了软件配置,具体如下:

请问我该如何解决这个问题,来实现CANFD的通信收发代码…

您好!

我正在使用TMS320F28388D的CANFD通信代码,我在使用官方提供的代码时发现问题如下:

我使用的例程是MCAN_ex3_loopback_syscfg;在下载程序后进行仿真发现代码卡在while循环里面:

具体位置如下:

在这个例程中我只修改了我的晶振时钟和引脚,由25MHz变为了20Mhz,引脚由原本的GPIO30…

我正在学习TMS320F280094,现在运行程序时(RAM与Flash都一样),只有在插着探针(XDS100V2)时才能正常运行,拔下后芯片就会停止运行(板子插着探针时,电流有0.09A,拔下后只有0.02A),重新插上后又能恢复正常运行,此时并没有进CCS的调试模式。

若断电后再上电,或者按下复位键,则需要重新烧录后才能正常工作。

选择的是运行方式选项来烧录…

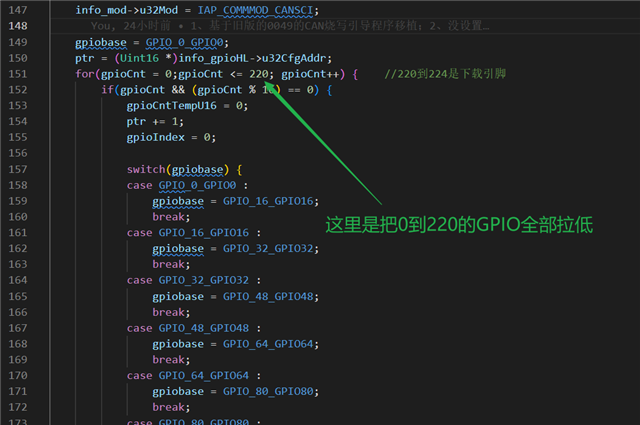

上图是对GPIO拉低处理,下载完之后,仿真器再进行连接就连接不上了,通过CAN可以看到有报文发出,说明芯片在运行

我使用XDS110仿真器,配置如下图所示

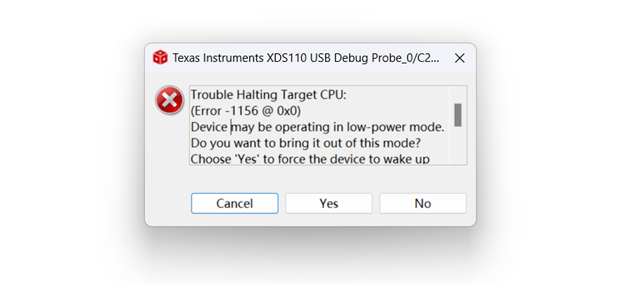

然后我就进行排查为什么连接不上,因为这个0道220GPIO全部拉低的功能是新添加的,所以我进行了仿真,当运行道205GPIO时就出现了如下的错误:

Trouble Halting Target CPU:(Error -1156 @ 0x0)Device may be operating in low…

刚开始学习C2000,现在在根据官方数据手册绘制核心板时,遇到一些困惑的点,如下:

PGA_GND理想设计应该是开尔文连接,这里的开尔文连接指的是什么,我可否直接接在核心板上的GND(连接的VSSA、VSS、VREFLOA、VREFLOB、VREFLOC)。

还有PGA_IN的端口在不使用的时候应该连接到VSS还是悬空即可。

在连接VREFHIB\VREFHIC和VREFHIA这两个ADC外置参考源时,我将这两个端口连接在一起,并连接2.2uF的陶瓷电容…

GPIO41设置为输入,无上下拉模式,芯片外部GPIO41通过电阻接GND,测试GPIO41对GND的电压为0.02V,输入寄存器GPIO41的状态是1,这是为何?

我在基于DSP 28075做程序加密时,遇到几个问题:

1、当 没有给程序加密时,BootLoader程序可以正常启动。

2、程序是基于BootLoader和应用程序两个部分,在加密完成后,程序BootLoader运行不起来,程序无法跳转到0x80000起始地址,一烧写程序总是进入非法中断。什么原因呢?

3、当在程序中连着仿真器,人为将PC指针指向0x80000地址时,程序可以正常运行;

在代码工程里某个.C文件定义几个变量:

Uint32_t ceshi6;

Uint32_t ceshi7;

Uint32_t ceshi8;

Uint32_t ceshi9;

Uint32_t ceshi10;

这几个变量仅仅定义不使用,代码执行一切正常。如果这几个函数不定义,则异常的现象是操作系统任务的主函数:

while(1)

{

event = OSEventPend();

if(event & (1 << eTaskEventTime)…

CCS版本:Code Composer Studio 12.8.1;

C2000ware :C2000Ware_5_04_00_00;

UniFlash :UniFlash 9.1.0;

硬件环境:开发套件;

C2000 实时 MCU F28P55X LaunchPad 开发套件;

工程背景:自己的工程基于".\C2000Ware_5_04_00_00…

CCS调试时,Load memory功能从外部文件向地址写入数据时,使用ram的地址可以修改数据,使用flash的地址显示Memory map prevented writing,修改gel文件,增加写权限后出现Memory verification failed. 我想请教一下,这个问题该怎么解决,还是说此功能只能在SRam的地址空间内操作

比如下图所示,我在ram申请了20 int大小的空间,使用Load Memory功能正常,数据可以更改

项目要求在SPI存储器中存储一个引导工程,和一个备份工程,以及一份正式程序,上电通过SPI引导自动启动引导程序,然后引导程序将正式程序从SPI存储器中搬移出来放置在RAM中运行,以上功能我已经在内部flash上实现了(通过配置CMD,然后引导功能跳转其他工程的codestart的方式),但是这个从SPI片外存储器上是真的不会搞,所以来这边求助一下大佬

CCSV12 版本,擦除设置选择擦除所有,但通过uniflash 工具读出来显示,实际大于0xc0000地址的数据没有擦除,导致烧录失败,检查其它设置都正常